# SF32LB52x

# User Manual

V0.8.8

UM5201-SF32LB52x-EN

SiFLi Technologies (Nanjing) Co., Ltd.

<http://www.sifli.com>

Copyright ©2025

## Revision History

### Document Status

| Document Status | Version Range | Description                                                                                                                                                                                                                                                        |

|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Draft           | 0.0.0 ~0.9.9  | Initial draft, informal release. The information is preliminary data, reflecting the specifications and performance of the product before mass production. No warranty is made as to the accuracy and the content is subject to change at any time without notice. |

| Release         | 1.0.0 ~1.9.9  | Official release, and minor amendments might be made to the information to more accurately reflect the specifications and performance of mass-produced products; SiFLi reserves the right to make changes to the document at any time without notice.              |

## Revision History

| Date       | Version | Release Notes                                                                                                                                                                                                                      |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2025-11-17 | 0.8.8   | Added Chapter2 Measurement and Calibration of Clocks                                                                                                                                                                               |

| 2025-09-23 | 0.8.7   | Added configuration for external PA and LNA                                                                                                                                                                                        |

| 2025-07-10 | 0.8.6   | Added AUDCODEC and Bluetooth Chapters                                                                                                                                                                                              |

| 2025-06-09 | 0.8.5   | Added power management architecture for 52X series.                                                                                                                                                                                |

| 2025-06-04 | 0.8.4   | Added the base address of register table and the overview of some modules.                                                                                                                                                         |

| 2025-05-28 | 0.8.3   | Added Default PD/PU Setting in Table 5-1 and updated Figure 3-1                                                                                                                                                                    |

| 2025-03-10 | 0.8.2   | Corrected the frame format content in the Debug Interface section and the endpoint description for USB. Corrected the description of the data bit width supported by SPI. Added access descriptions for 0x10000000 and 0x60000000. |

| 2025-03-05 | 0.8.1   | Modified the description of the Cordic coprocessor.                                                                                                                                                                                |

| 2025-03-03 | 0.8     | Added a Debug Interface section, detailing the relationship between various modules and the system clock in the clock and reset section. Included the USART module and RTC register table.                                         |

| 2025-01-10 | 0.7     | Add a description of the combined IO and an overview of each IP.                                                                                                                                                                   |

| 2024-12-20 | 0.6     | Update LCDC, EFUSE and other modules                                                                                                                                                                                               |

| 2024-12-06 | 0.5     | Update the sections on clock and reset, low power consumption, etc.                                                                                                                                                                |

| 2024-11-06 | 0.4     | Update relevant information on GPADC                                                                                                                                                                                               |

| 2024-06-11 | 0.3     | Updated information related to the small core                                                                                                                                                                                      |

| 2023-07-06 | 0.2     | Correct power consumption values and update the AON register table and DMA section content                                                                                                                                         |

| 2023-06-15 | 0.1     | Draft                                                                                                                                                                                                                              |

## Overview

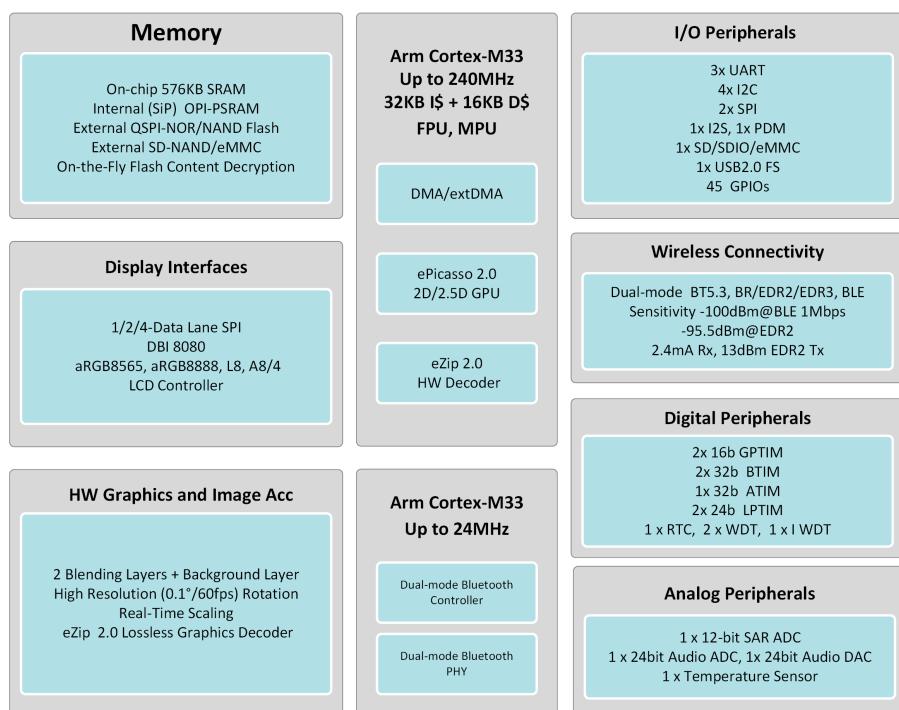

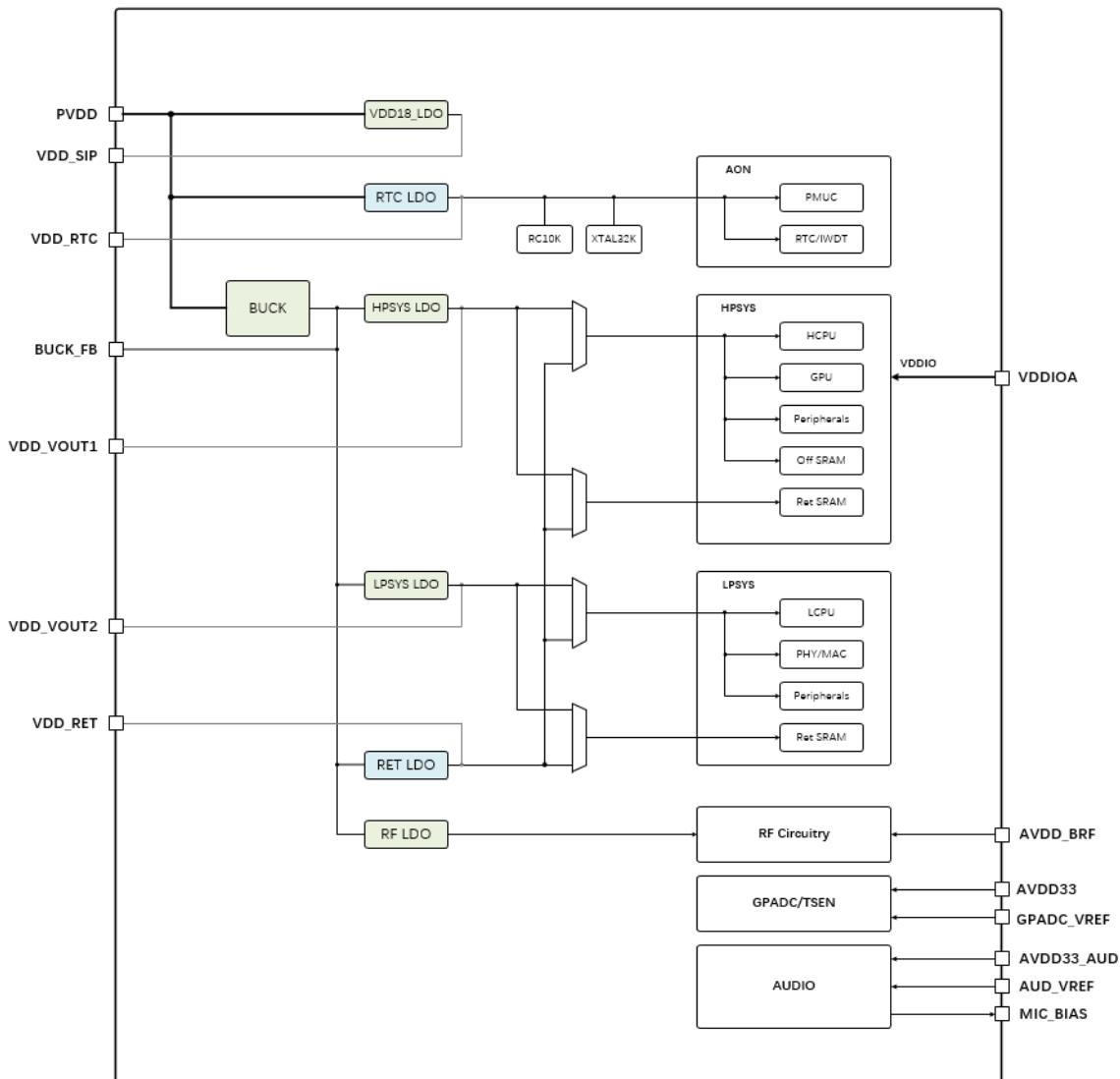

SF32LB52x is a family of highly integrated high-performance MCUs designed for ultra-low power Artificial Intelligence of Things (AIoT) scenarios. SF32LB52x adopts the big.LITTLE architecture with Arm Cortex-M33 STAR-MC1 processors, and is embedded with 2D/2.5D GPU, dual-mode BT5.3, and audio codec. SF32LB52x can be used for a wide variety of applications such as wearables, smart HMI devices, and smart homes.

The high-performance processor ("big core") of SF32LB52x can operate at up to 240MHz for 984 CoreMark. It supports dynamic frequency power adjustment, can also serve as sensor hub and Bluetooth controller at high power efficiency of 4.8uA/CoreMark, thus delivering no-compromise user experience of both high computational performance required for feature-rich graphical HMI (Human Machine Interface) and ultra-

low power sensor hub operation.

The 2D/2.5D GPU, at up to 240MHz, supports 2-layer alpha blending, hardware accelerated rotation and scaling, and conversion of common graphic formats. eZip™2.0 supports lossless compressed graphics file, saving memory bandwidth and storage capacity. The LCD controller can support interfaces of 8080/QSPI at a full-screen refresh frame rate up to 60fps, and support Always-On Display.

The dual-mode BT5.3 transceiver has a maximum Tx power of 13dBm at EDR2 mode and Rx power of 2.4mA@3.8V, and the sensitivity reaches -100dBm (1Mbps) for BLE and -95.5dBm for EDR2. SF32LB52x is embedded with high-fidelity audio ADC/DAC, supporting Bluetooth call and connecting headphones for MP3 playback.

## Functional Block Diagram

Figure 0-1: Functional Block Diagram

## Features

### CPU and Memory

- High Performance Processor (HCPU)

- Arm Cortex-M33 STAR-MC1

- Up to 240MHz clock frequency, adjustable

- Up to 370DMIPS, 984 EEMBC CoreMark

- I-Cache + D-Cache: 32KB(2-way)+16KB(4-way)

- SRAM: 512KB (All Retention SRAM)

- CoreMark power: 23uA/MHz @3.8V

- Single Precision Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Ultra Low-Power Processor (LCPU)

- Arm Cortex-M33 STAR-MC1

- Up to 24MHz clock frequency, adjustable

- SRAM: 64KB (All Retention SRAM)

### Wireless Connectivity

- Dual-mode BT5.3, support BLE Audio

- Sensitivity: -100dBm(BLE/1Mbps), -96.3dBm(BR), -95.5dBm(EDR2)

- Max. Tx power: 13dBm (EDR2/3) , 19dBm (BR/BLE)

- Rx peak current (BR): 2.4mA@3.8V

### Audio

- 1×HiFi 24-bit Audio DAC

- Noise floor: 3.7uVrms

- SNR(with 10kohm load and A-Weighted): 109dB, Dynamic Range: 109dB

- Sample rate: 8k/ 16k/ 11.025k/ 22.05k/ 24k/ 32k/ 44.1k/ 48kHz

- Support digital volume of 192 steps with zero-crossing detection

- 1×HiFi 24-bit Audio ADC

- SNR(A-Weighted): 99dB, Dynamic Range: 99dB

- Sample rate: 8k/ 11.025k/ 12k/ 16k/ 22.05k/ 24k/ 32k/ 44.1k/ 48kHz

- A digital high-pass filter can be used to remove dc offsets of ADC

- Support single-ended and fully differential input microphones

- Micbias LDO with 1.4V~2.8V output voltage and 0~2mA output current

### Graphics and Display

- 2D/2.5D GPU—ePicasso™2.0

- Hardware-accelerated rotation, scaling, and mirroring

- Max. resolution: 512×512

- Support aRGB8565, aRGB8888, L8, A8/4/2,YUV, support alpha blending

- Lossless Decompression Accelerator – eZip™2.0

- Lossless graphics decompression

- support native animation eZip-A

- Concatenated operation with ePicasso™2.0

- LCD Controller

- Support 8080, SPI, Dual-SPI, Quad-SPI

- 1 layer + 1 background layer alpha blending

- Independent LCD controller, Always-On Display

### Memory Interface

- Support (SiP) NOR-Flash, interface frequency up to 96MHz

- Support (SiP) OPI-PSRAM, interface frequency up to 144MHz

- 1×MPI(QSPI), support NOR, NAND, QPI-PSRAM

- 1×SD/SDIO, support SD3.0, SDIO3.0, eMMC

### DMA

- General DMA: high efficiency data transfer between internal memory and peripherals

- extDMA: high efficiency data transfer between internal memory and external memory

### Security

- AES, HASH and CRC hardware accelerators

- True random number generator (TRNG)

- PSA Certified Level 1

### Timers

- 2×16b GPTIM, 2×32b BTIM, 1×32b ATIM, 2×24b LPTIM

- 1×RTC

- 2×24b WDT, 1×IWDT

### Analog Peripherals

- 1×12-bit general purpose SAR ADC, 8 channels

- 1×Temperature sensor

- 1×24-bit audio ADC, 1×24-bit audio DAC

#### I/O Peripherals

- Up to 45 GPIOs

- 3×UART, 4×I<sup>2</sup>C, 2×SPI

- 1×I<sup>2</sup>S, 1×PDM

- 1×USB2.0 FS

- Peripheral Task Controller (PTC)

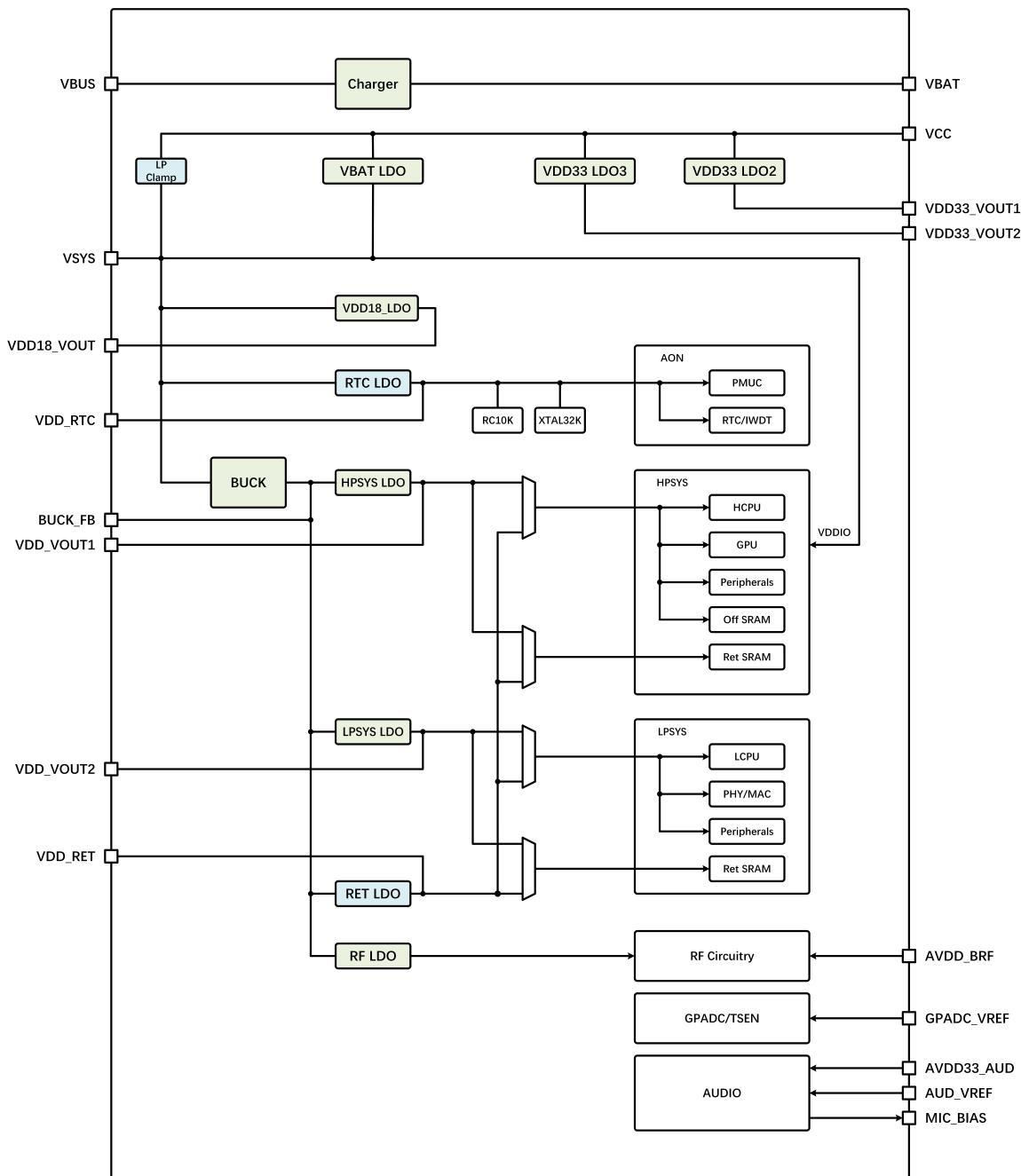

#### Power Management

- High-efficiency buck and low-power LDO

- 2 external 3.3V power supply LDOs, Max. current 150mA×2

- Sleep current: 2uA

- Built-in 560mA lithium battery linear charger, supporting 4.2V-4.45V full voltage

- VBAT voltage range: 3.2V-4.7V

- VBUS voltage range: 4.6V-5.5V

#### Others

- Operating Temperature Range: -40~85°C

- Package: QFN68L, 44 GPIOs, 7×7×0.85mm

## Applications

### Smart Wearable

- Smart watch

- Smart wristband

- Wearable medical device

- Fitness equipment

### Industrial Device

- Cost-effective display solution

- Graphical Human-Machine Interface (HMI) device

- Industrial sensor hub

- Industrial equipment monitoring

- Industrial instrumentation

### Vehicle Device

- Electric vehicle control center

- Car key

- Wearable car remote controls

### Home Automation

- Smart home appliance

- Smart door lock

### Generic Scenario

- Low-power sensor hub

- Bluetooth mesh

## Contents

|                                                                    |           |                                                                                |           |

|--------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------|-----------|

| <b>Revision History</b>                                            | <b>i</b>  | 3.1 SF32LB52x Lithium Batter-powered Version(520/523/525/527,et.) . . . . .    | <b>25</b> |

| <b>Overview</b>                                                    | <b>ii</b> | 3.2 SF32LB52X Conventional Power Supply Version(52B/52E/52G/52J,et.) . . . . . | <b>28</b> |

|                                                                    |           | 3.3 Charging Module . . . . .                                                  | <b>30</b> |

|                                                                    |           | 3.4 PMUC Register . . . . .                                                    | <b>31</b> |

| <b>1 Introduction</b>                                              | <b>1</b>  | <b>4 Low Power Mode</b>                                                        | <b>39</b> |

| 1.1 System Architecture . . . . .                                  | 1         | 4.1 Introduction . . . . .                                                     | 39        |

| 1.2 Cortex-M33 STAR-MC1 Processor . . . . .                        | 1         | 4.2 Summary of Main Operating Mode . . . . .                                   | 39        |

| 1.3 High-Performance Processor (Big Core) System (HPSYS) . . . . . | 2         | 4.2.1 Active Mode . . . . .                                                    | 39        |

| 1.3.1 Bus Architecture . . . . .                                   | 2         | 4.2.2 Sleep Mode . . . . .                                                     | 40        |

| 1.3.2 Memory Type . . . . .                                        | 2         | 4.2.3 Deepsleep Mode . . . . .                                                 | 40        |

| 1.3.2.1 Cache . . . . .                                            | 2         | 4.2.4 Standby Mode . . . . .                                                   | 41        |

| 1.3.2.2 TCM . . . . .                                              | 2         | 4.2.5 Hibernate Mode . . . . .                                                 | 42        |

| 1.3.2.3 SRAM . . . . .                                             | 3         | 4.2.6 Debugger Behavior in Low Power Mode . . . . .                            | 43        |

| 1.3.2.4 Off-chip RAM . . . . .                                     | 3         | 4.2.7 Determining the Current Low Power Mode . . . . .                         | 43        |

| 1.3.2.5 Off-chip Flash . . . . .                                   | 3         | 4.3 HPSYS_AON Register . . . . .                                               | 44        |

| 1.3.3 Address Mapping . . . . .                                    | 3         | <b>5 Input and Output</b>                                                      | <b>48</b> |

| 1.3.4 Interrupt List . . . . .                                     | 4         | 5.1 Introduction . . . . .                                                     | 48        |

| 1.4 Bus Access Permissions . . . . .                               | 6         | 5.2 IO Structure . . . . .                                                     | 48        |

| <b>2 Clock and Reset</b>                                           | <b>7</b>  | 5.3 Input and Output Selection . . . . .                                       | 49        |

| 2.1 Introduction . . . . .                                         | 7         | 5.4 IO High Impedance . . . . .                                                | 49        |

| 2.2 Reset Sources . . . . .                                        | 7         | 5.5 GPIO Output . . . . .                                                      | 49        |

| 2.2.1 Board-Level Reset Sources . . . . .                          | 7         | 5.6 GPIO Input . . . . .                                                       | 50        |

| 2.2.2 Watchdog Reset Source . . . . .                              | 7         | 5.7 IO Function List . . . . .                                                 | 51        |

| 2.2.3 Software Reset Source . . . . .                              | 8         | 5.8 Integrated IO . . . . .                                                    | 57        |

| 2.2.4 Wake-Up Reset Sources . . . . .                              | 8         | 5.9 Low Power IO . . . . .                                                     | 58        |

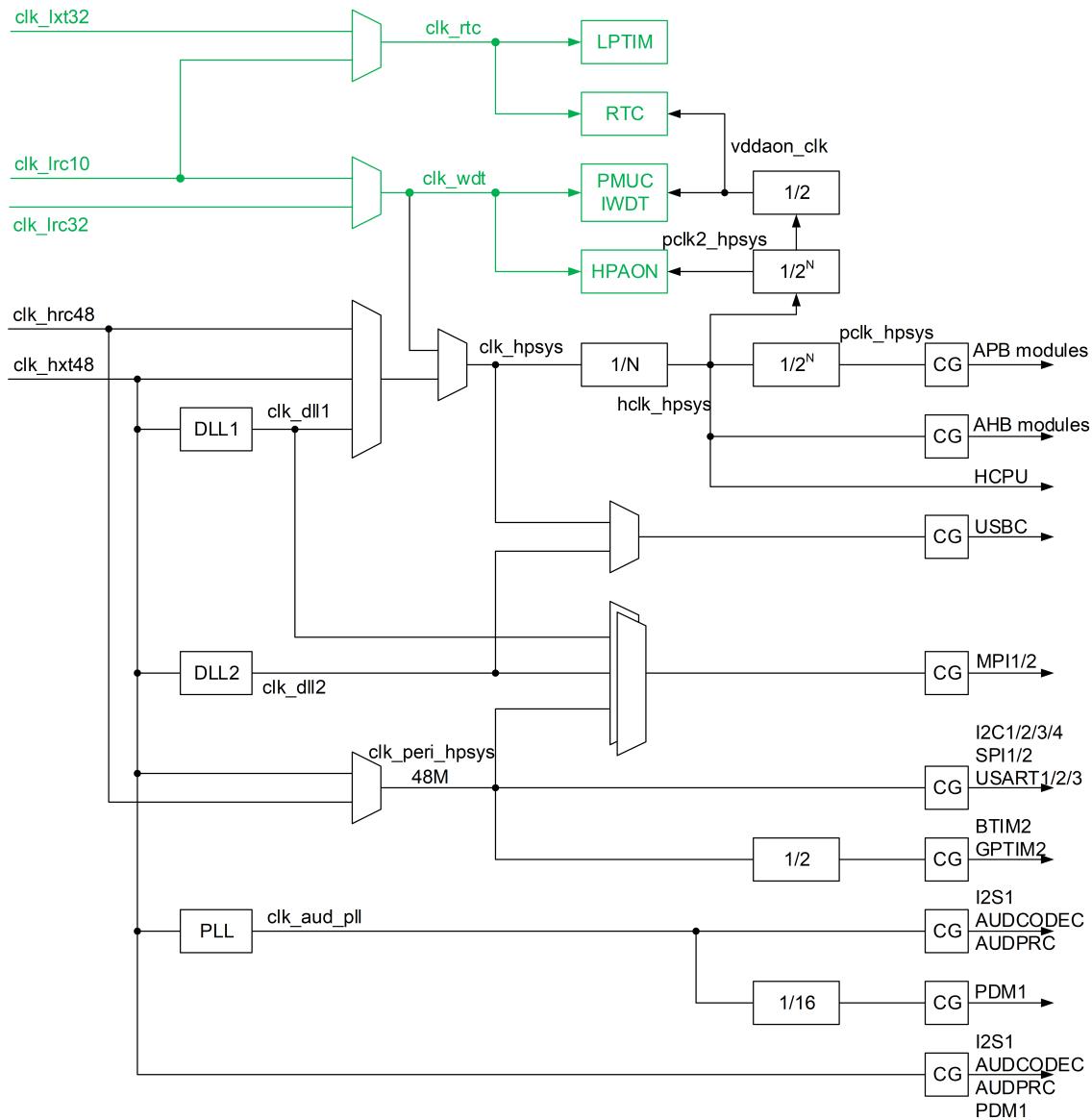

| 2.3 Clock Source . . . . .                                         | 9         | 5.10 IO Power Supply . . . . .                                                 | 58        |

| 2.4 System Clock Structure . . . . .                               | 11        | 5.11 Wake-Up PIN . . . . .                                                     | 58        |

| 2.5 Module clock . . . . .                                         | 13        | 5.12 IO Status in Low Power Mode . . . . .                                     | 59        |

| 2.6 Module Enablement . . . . .                                    | 14        | 5.13 Avoid IO Leakage . . . . .                                                | 60        |

| 2.7 Module Reset . . . . .                                         | 15        | 5.14 Avoid Leakage in Integrated IO . . . . .                                  | 62        |

| 2.8 Measurement and Calibration of Clocks . . . . .                | 15        | 5.15 HPSYS_PINMUX Register . . . . .                                           | 62        |

| 2.8.1 Measurement and Calibration of clk_hxt48 . . . . .           | 15        | 5.16 HPSYS_CFG Register . . . . .                                              | 75        |

| 2.8.2 Measurement and Calibration of clk_hrc48 . . . . .           | 16        | 5.17 HPSYS_GPIO Register . . . . .                                             | 82        |

| 2.8.3 Measurement of clk_lxt32 . . . . .                           | 16        | <b>6 DMA</b>                                                                   | <b>85</b> |

| 2.8.4 Measurement of clk_lrc10 . . . . .                           | 17        | 6.1 DMAC . . . . .                                                             | 85        |

| 2.9 HPSYS_RCC Register . . . . .                                   | 17        | 6.1.1 Introduction . . . . .                                                   | 85        |

| <b>3 Power Management</b>                                          | <b>25</b> | 6.1.2 Main Features . . . . .                                                  | 85        |

|                                                                    |           | 6.1.3 Peripheral Requests . . . . .                                            | 85        |

|                                                                    |           | 6.1.4 DMAC Function Description . . . . .                                      | 87        |

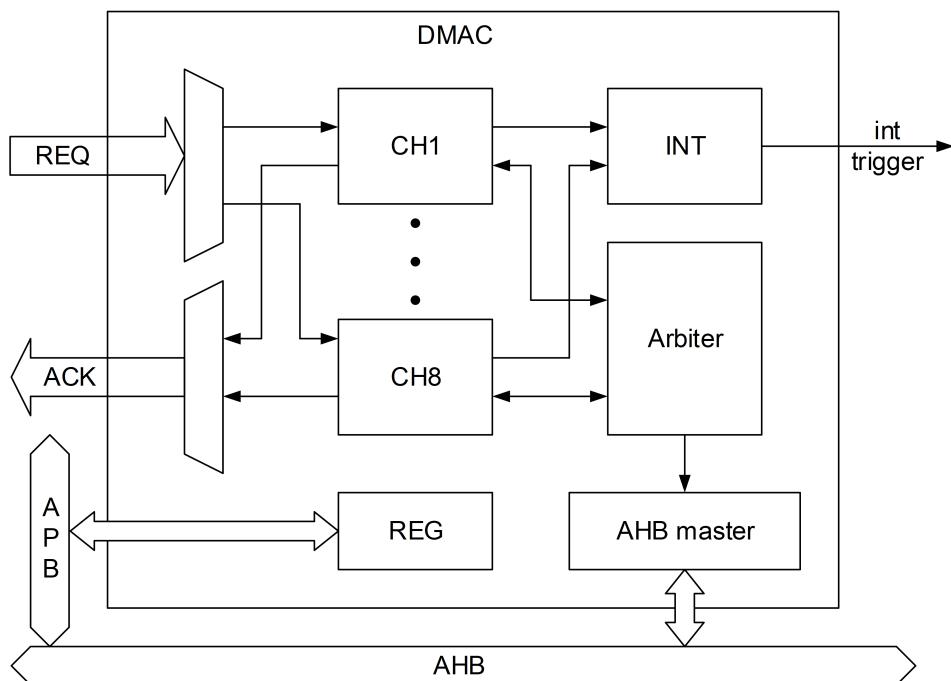

|                                                                    |           | 6.1.4.1 DMAC Block Diagram . . . . .                                           | 87        |

|                                                                    |           | 6.1.4.2 Transfer Efficiency . . . . .                                          | 87        |

|          |                                           |            |          |                                             |            |

|----------|-------------------------------------------|------------|----------|---------------------------------------------|------------|

| 6.1.4.3  | Transfer Mode . . . . .                   | 88         | 7.1.3.9  | Slave Transmisson process . . . . .         | 119        |

| 6.1.4.4  | Transmission Process . .                  | 88         | 7.1.3.10 | Slave receiving process                     | 119        |

| 6.1.4.5  | Transfer Enable . . . . .                 | 88         | 7.1.3.11 | DMA Transfer . . . . .                      | 120        |

| 6.1.4.6  | Transfer Unit . . . . .                   | 88         | 7.1.3.12 | Bus Exception Recovery                      | 120        |

| 6.1.4.7  | Transfer Quantity . . . .                 | 89         | 7.1.4    | I2C Registers . . . . .                     | 121        |

| 6.1.4.8  | Circular Mode . . . . .                   | 89         | 7.2      | SPI . . . . .                               | 126        |

| 6.1.4.9  | Transmission Direction .                  | 89         | 7.2.1    | Introduction . . . . .                      | 126        |

| 6.1.4.10 | Transmission Bit Width                    | 89         | 7.2.2    | Main Features . . . . .                     | 127        |

| 6.1.4.11 | Transmission Address .                    | 90         | 7.2.3    | Interface Signals . . . . .                 | 127        |

| 6.1.4.12 | Channel Arbitration . .                   | 90         | 7.2.4    | FIFO . . . . .                              | 128        |

| 6.1.4.13 | Block Transfer . . . . .                  | 91         | 7.2.5    | Data Format . . . . .                       | 128        |

| 6.1.4.14 | Notifcation Mechanism                     | 91         | 7.2.5.1  | Related System Resources . . . . .          | 133        |

| 6.1.4.15 | Channel Configuration Process . . . . .   | 91         | 7.2.5.2  | Communication Process                       | 133        |

| 6.1.4.16 | Transfer Completion Handling . . . . .    | 91         | 7.2.5.3  | Receive-Only Mode . .                       | 135        |

| 6.1.5    | DMAC Register . . . . .                   | 92         | 7.2.5.4  | Three-Wire Mode . .                         | 135        |

| 6.2      | ExtDMA . . . . .                          | 112        | 7.2.6    | SPI Register . . . . .                      | 135        |

| 6.2.1    | Introduction . . . . .                    | 112        | 7.3      | PTC . . . . .                               | 140        |

| 6.2.2    | Main Features . . . . .                   | 112        | 7.3.1    | Introduction . . . . .                      | 140        |

| 6.2.3    | Function Description . . . . .            | 112        | 7.3.2    | Main Features . . . . .                     | 141        |

| 6.2.3.1  | Transfer Effciency . . .                  | 112        | 7.3.3    | Function Description . . . . .              | 141        |

| 6.2.3.2  | Data Address and Bit Width . . . . .      | 112        | 7.3.3.1  | Channel Trigger . . . . .                   | 141        |

| 6.2.3.3  | Transfer Enable . . . . .                 | 112        | 7.3.3.2  | Channel Tasks . . . . .                     | 142        |

| 6.2.3.4  | Transfer Quantity . . . .                 | 113        | 7.3.3.3  | Channel Arbitration . .                     | 143        |

| 6.2.3.5  | Notifcation Mechanism                     | 113        | 7.3.4    | PTC Register . . . . .                      | 143        |

| 6.2.3.6  | Exception Handling . .                    | 113        | 7.4      | USART . . . . .                             | 150        |

| 6.2.3.7  | Recommended Configuration Process . . . . | 113        | 7.4.1    | USART Register . . . . .                    | 151        |

| 6.2.4    | ExtDMA Register . . . . .                 | 113        | 7.5      | USB . . . . .                               | 156        |

| <b>7</b> | <b>Connecting Peripheral</b>              | <b>116</b> | <b>8</b> | <b>Analog Peripheral</b>                    | <b>157</b> |

| 7.1      | I2C . . . . .                             | 116        | 8.1      | GPADC . . . . .                             | 157        |

| 7.1.1    | Introduction . . . . .                    | 116        | 8.1.1    | Introduction . . . . .                      | 157        |

| 7.1.2    | Main Features . . . . .                   | 116        | 8.1.2    | Main Features . . . . .                     | 157        |

| 7.1.3    | I2C Function Description . . . . .        | 117        | 8.1.3    | Function Description . . . . .              | 158        |

| 7.1.3.1  | Two-Wire Transmission                     | 117        | 8.1.3.1  | GPADC Clock Generation                      | 158        |

| 7.1.3.2  | Input Filter . . . . .                    | 117        | 8.1.3.2  | Time Slot Configuration                     | 158        |

| 7.1.3.3  | Transmission Rate . . .                   | 117        | 8.1.3.3  | Single-Ended/Differential Mode . . . . .    | 158        |

| 7.1.3.4  | Transmission sequence                     | 118        | 8.1.3.4  | Input Channel Selection                     | 158        |

| 7.1.3.5  | Operating Modes and States . . . . .      | 118        | 8.1.3.5  | Sampling Mode . . . . .                     | 158        |

| 7.1.3.6  | I2C Initialization Process                | 118        | 8.1.3.6  | Activate the GPADC . .                      | 159        |

| 7.1.3.7  | Master Transmission Process . . . . .     | 118        | 8.1.3.7  | Data Access . . . . .                       | 159        |

| 7.1.3.8  | Master Receiving Process                  | 119        | 8.1.3.8  | Notifcation Mechanism                       | 160        |

|          |                                           |            | 8.1.3.9  | System Configuration Dependencies . . . . . | 160        |

|                                                            |            |                                            |     |

|------------------------------------------------------------|------------|--------------------------------------------|-----|

| 8.1.3.10 Configuration Startup Process . . . . .           | 160        | 9.2.3.4 Master-Slave Mode . . . . .        | 198 |

| 8.1.4 GPADC Register . . . . .                             | 161        | 9.2.3.5 One Pulse Mode . . . . .           | 199 |

| 8.2 TSEN . . . . .                                         | 164        | 9.2.3.6 Timer Synchronization . . . . .    | 199 |

| 8.2.1 Introduction . . . . .                               | 164        | 9.2.3.7 Notifcation Mechanism . . . . .    | 199 |

| 8.2.2 Main Features . . . . .                              | 164        | 9.2.4 BTIM Register . . . . .              | 199 |

| 8.2.3 Function Description . . . . .                       | 164        | 9.3 GPTIM . . . . .                        | 202 |

| 8.2.3.1 Clock Signal . . . . .                             | 164        | 9.3.1 Introduction . . . . .               | 202 |

| 8.2.3.2 Reading Process . . . . .                          | 164        | 9.3.2 Main Features . . . . .              | 203 |

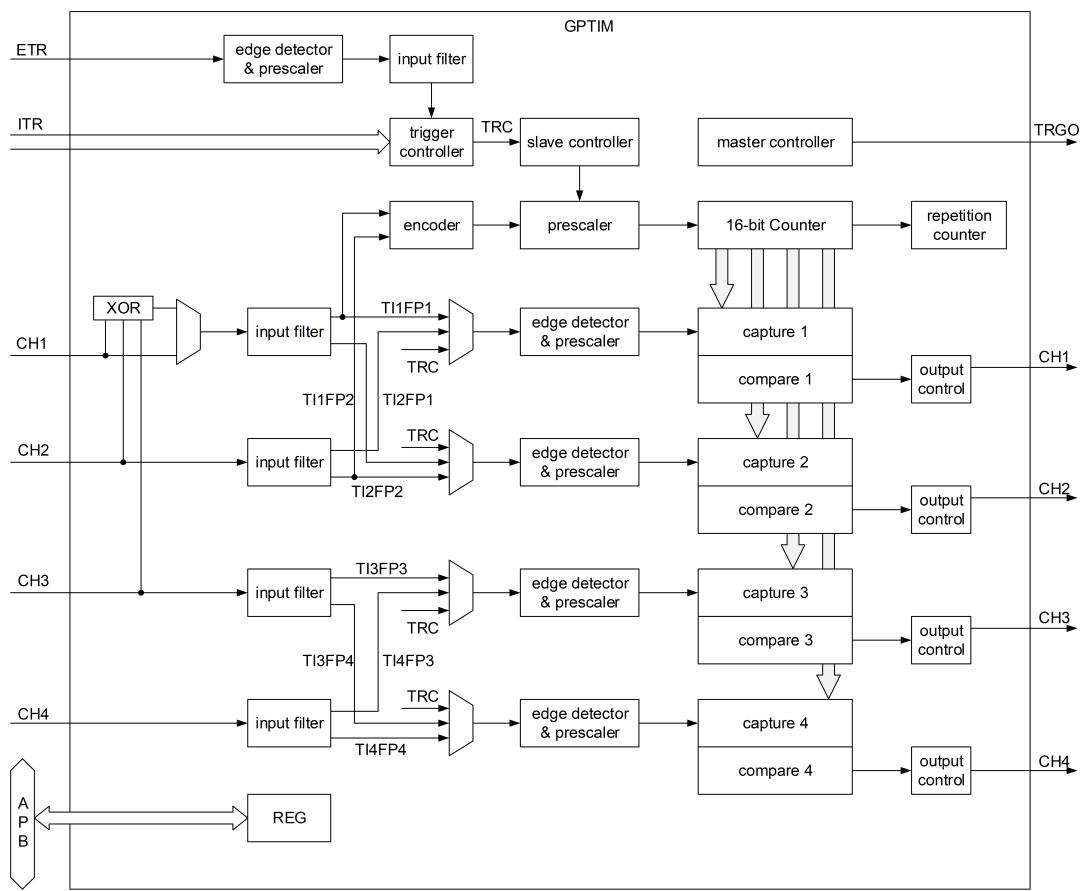

| 8.2.3.3 Usage Process . . . . .                            | 164        | 9.3.3 GPTIM Function Description . . . . . | 204 |

| 8.2.4 TSEN Register . . . . .                              | 165        | 9.3.3.1 Counter . . . . .                  | 204 |

| <b>9 Timer</b> . . . . .                                   | <b>166</b> | 9.3.3.2 Update Event(UEV) . . . . .        | 205 |

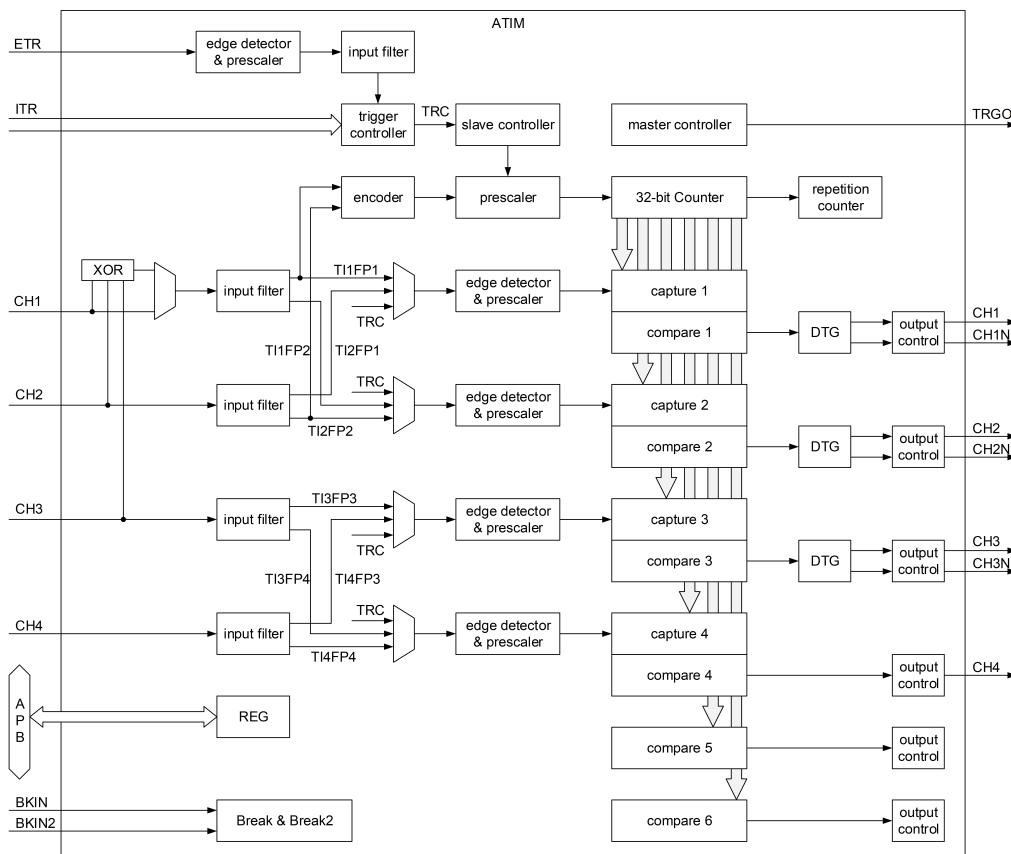

| 9.1 ATIM . . . . .                                         | 166        | 9.3.3.3 Repeat Counting . . . . .          | 205 |

| 9.1.1 Introduction . . . . .                               | 166        | 9.3.3.4 Shadow Register . . . . .          | 205 |

| 9.1.2 Main Features . . . . .                              | 166        | 9.3.3.5 Master-Slave Mode . . . . .        | 205 |

| 9.1.3 ATIM Function Description . . . . .                  | 168        | 9.3.3.6 Channel Input and Output . . . . . | 206 |

| 9.1.3.1 Counter . . . . .                                  | 168        | 9.3.3.7 Input Capture Mode . . . . .       | 206 |

| 9.1.3.2 Update Event(UEV) . . . . .                        | 168        | 9.3.3.8 PWM Input Capture . . . . .        | 207 |

| 9.1.3.3 Repeated Counting . . . . .                        | 168        | 9.3.3.9 Output Compare Mode . . . . .      | 208 |

| 9.1.3.4 Shadow Register . . . . .                          | 169        | 9.3.3.10 Basic PWM Output . . . . .        | 208 |

| 9.1.3.5 Master-Slave Mode . . . . .                        | 169        | 9.3.3.11 Asymmetric PWM output . . . . .   | 209 |

| 9.1.3.6 Channel Input and Output . . . . .                 | 169        | 9.3.3.12 Combined PWMO utput . . . . .     | 209 |

| 9.1.3.7 Input Capture Mode . . . . .                       | 170        | 9.3.3.13 One Pulse Mode . . . . .          | 210 |

| 9.1.3.8 PWM Input Capture . . . . .                        | 171        | 9.3.3.14 Encoder Interface Mode . . . . .  | 211 |

| 9.1.3.9 Output Compare Mode . . . . .                      | 171        | 9.3.3.15 Timer Synchronization . . . . .   | 212 |

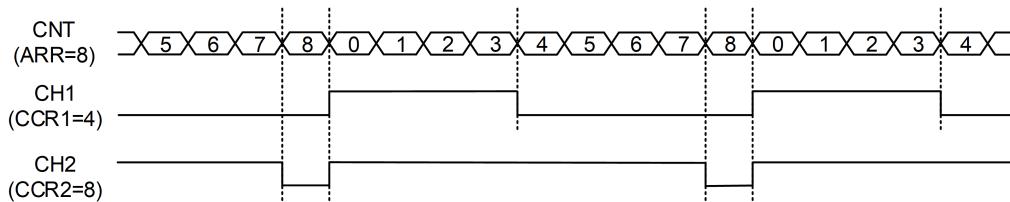

| 9.1.3.10 Basic PWM Output . . . . .                        | 172        | 9.3.3.16 Notification Mechanism . . . . .  | 212 |

| 9.1.3.11 Asymmetric PWM Out-put . . . . .                  | 172        | 9.3.4 GPTIM Register . . . . .             | 212 |

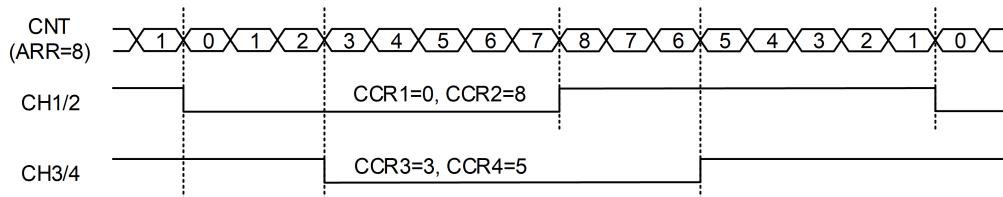

| 9.1.3.12 Combined PWM Output . . . . .                     | 173        | 9.3.5 Timer Cascading . . . . .            | 224 |

| 9.1.3.13 Complementary PWM output with dead time . . . . . | 174        | 9.4 LPTIM . . . . .                        | 224 |

| 9.1.3.14 Emergency Cut-off . . . . .                       | 174        | 9.4.1 Introduction . . . . .               | 225 |

| 9.1.3.15 6 Step PWM . . . . .                              | 175        | 9.4.2 Main Features . . . . .              | 225 |

| 9.1.3.16 One Pulse Mode . . . . .                          | 175        | 9.4.3 LPTIM function description . . . . . | 226 |

| 9.1.3.17 Encoder Interface Mode . . . . .                  | 175        | 9.4.3.1 counter . . . . .                  | 226 |

| 9.1.3.18 Timer Synchronization . . . . .                   | 176        | 9.4.3.2 Counting Clock . . . . .           | 226 |

| 9.1.3.19 Notifcation Mechanism . . . . .                   | 177        | 9.4.3.3 Update Event(UEV) . . . . .        | 227 |

| 9.1.4 ATIM Register . . . . .                              | 177        | 9.4.3.4 Repeat Counting . . . . .          | 227 |

| 9.2 BTIM . . . . .                                         | 196        | 9.4.3.5 Counter Trigger . . . . .          | 227 |

| 9.2.1 Introduction . . . . .                               | 197        | 9.4.3.6 Timeout Monitoring . . . . .       | 227 |

| 9.2.2 Main Features . . . . .                              | 197        | 9.4.3.7 PWM Output . . . . .               | 227 |

| 9.2.3 BTIM Function Description . . . . .                  | 197        | 9.4.3.8 Notifcation Mechanism . . . . .    | 228 |

| 9.2.3.1 Counter . . . . .                                  | 197        | 9.4.4 LPTIM Register . . . . .             | 228 |

| 9.2.3.2 Update Event(UEV) . . . . .                        | 198        | 9.5 WDT . . . . .                          | 233 |

| 9.2.3.3 Shadow Register . . . . .                          | 198        | 9.5.1 Introduction . . . . .               | 233 |

|           |                                                           |            |           |                                                                  |            |

|-----------|-----------------------------------------------------------|------------|-----------|------------------------------------------------------------------|------------|

| 9.5.3     | WDT Register . . . . .                                    | 235        | 11.3.5    | Audprc Register . . . . .                                        | 277        |

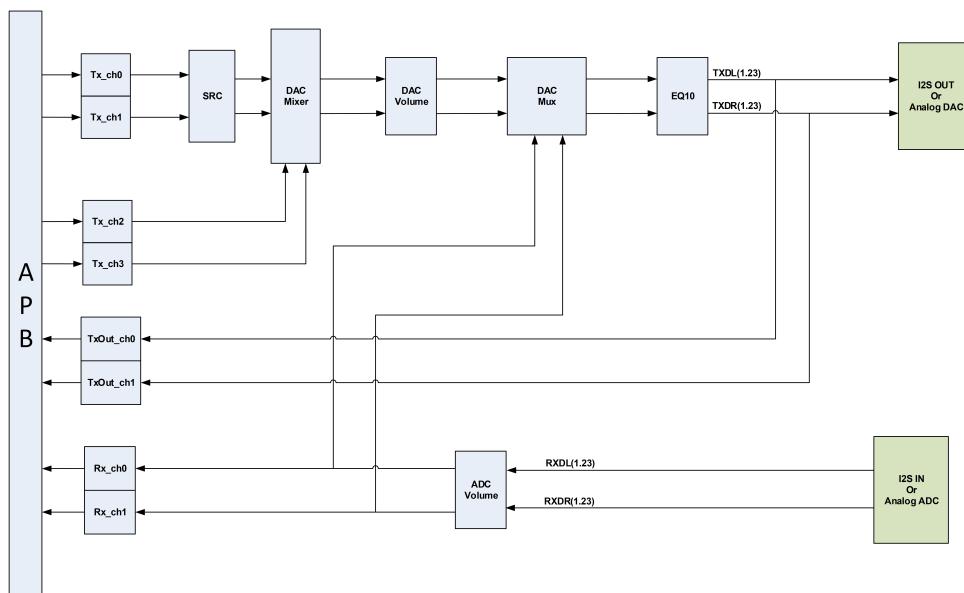

| 9.6       | RTC . . . . .                                             | 236        | 11.4      | Audcodec . . . . .                                               | 287        |

| 9.6.1     | RTC Register . . . . .                                    | 236        | 11.4.1    | Module Function . . . . .                                        | 287        |

| <b>10</b> | <b>Graphics</b>                                           | <b>242</b> | 11.4.2    | Path Structure . . . . .                                         | 288        |

| 10.1      | ePicasso™ High-Performance 2.5D Graphics Engine . . . . . | 242        | 11.4.3    | Function Description of Each Module . . . . .                    | 288        |

| 10.1.1    | Layer Overlay . . . . .                                   | 242        | 11.4.3.1  | Power Supply Module . . . . .                                    | 288        |

| 10.1.2    | Graphic Scaling . . . . .                                 | 242        | 11.4.3.2  | Clk Module . . . . .                                             | 288        |

| 10.1.3    | Graphic Rotation . . . . .                                | 242        | 11.4.3.3  | ADC Module . . . . .                                             | 288        |

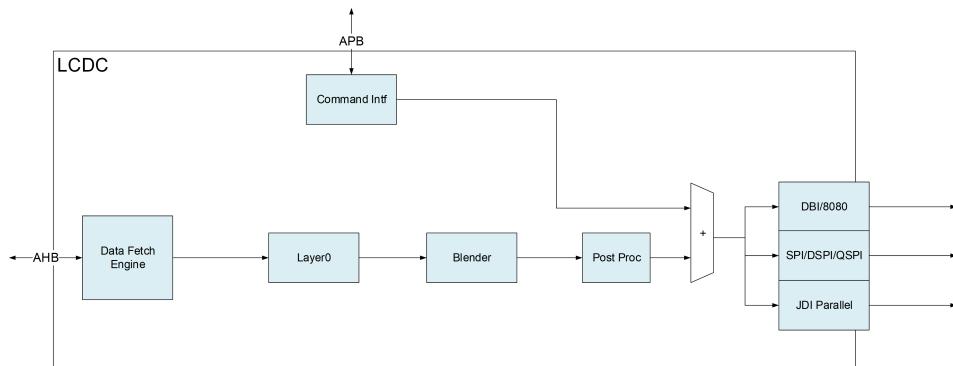

| 10.2      | LCDC . . . . .                                            | 242        | 11.4.3.4  | DAC Module . . . . .                                             | 288        |

| 10.2.1    | Introduction . . . . .                                    | 242        | 11.4.4    | Audcodec Configuration Process . . . . .                         | 288        |

| 10.2.2    | Architecture Introduction . . . . .                       | 243        | 11.4.4.1  | Configuration of the Power Supply . . . . .                      | 289        |

| 10.2.3    | Configuration Process . . . . .                           | 243        | 11.4.4.2  | Configuration of the Clk . . . . .                               | 289        |

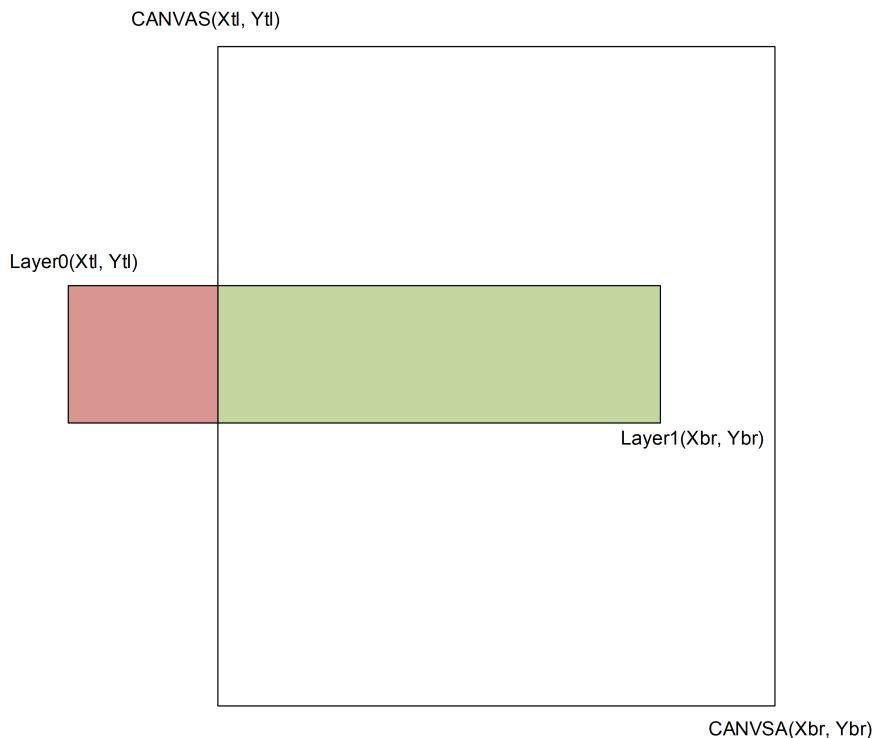

| 10.2.3.1  | Layer Configuration . . . . .                             | 243        | 11.4.4.3  | ADC Configuration . . . . .                                      | 289        |

| 10.2.3.2  | Interface Configuration . . . . .                         | 244        | 11.4.4.4  | DAC Configuration . . . . .                                      | 289        |

| 10.2.4    | LCDC Register . . . . .                                   | 246        | 11.4.5    | Audcodec Register . . . . .                                      | 289        |

| 10.3      | eZip™ Lossless Compression Decoder . . . . .              | 256        | 11.4.5.1  | Audcodec Register . . . . .                                      | 289        |

| <b>11</b> | <b>Audio</b>                                              | <b>258</b> | <b>12</b> | <b>Accelerator</b>                                               | <b>301</b> |

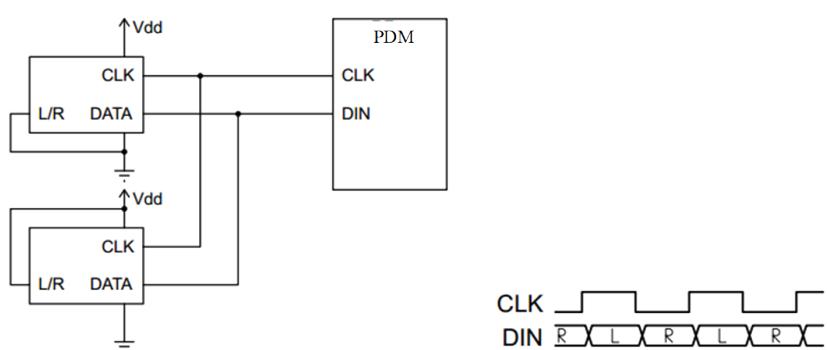

| 11.1      | PDM . . . . .                                             | 258        | 12.1      | Digital Signal Processing Accelerator . . . . .                  | 301        |

| 11.1.1    | Introduction . . . . .                                    | 258        | 12.1.1    | Cordic Co-Processor . . . . .                                    | 301        |

| 11.1.2    | Usage Instruction . . . . .                               | 258        | 12.2      | CRC . . . . .                                                    | 301        |

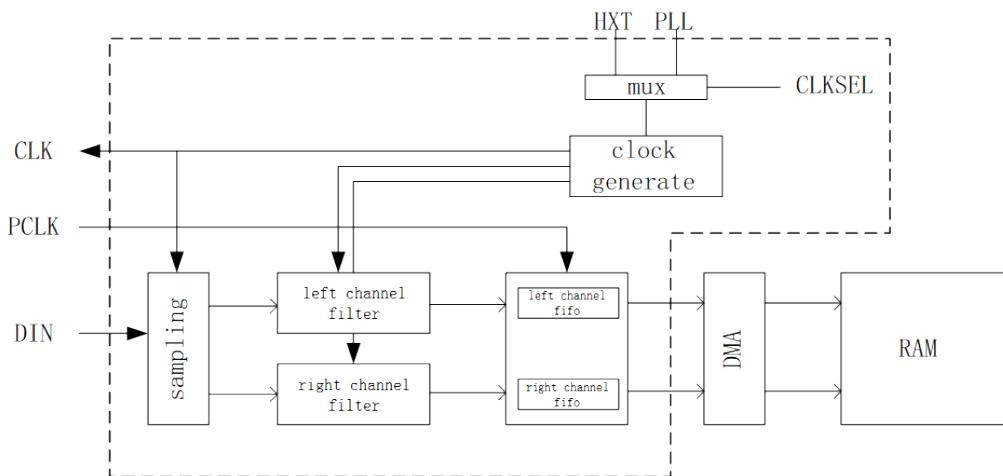

| 11.1.2.1  | Overall Structure of the PDM Module . . . . .             | 259        | 12.2.1    | Introduction . . . . .                                           | 301        |

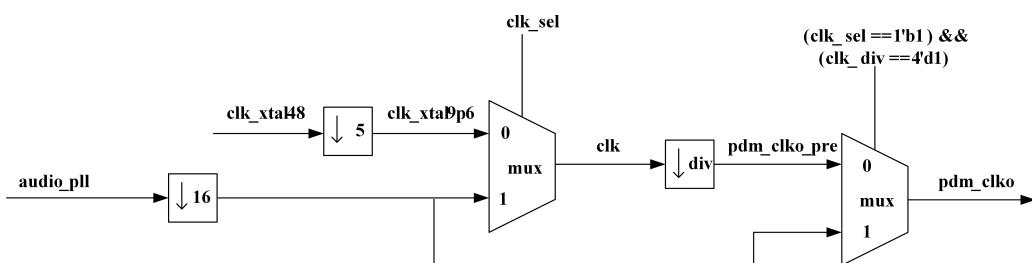

| 11.1.2.2  | Clock Structure of the PDM Module . . . . .               | 259        | 12.2.2    | Main Features . . . . .                                          | 301        |

| 11.1.2.3  | Precaution . . . . .                                      | 262        | 12.2.3    | CRC Configuration Method . . . . .                               | 301        |

| 11.1.3    | PDM Register . . . . .                                    | 262        | 12.2.4    | Data Format . . . . .                                            | 302        |

| 11.2      | I2S . . . . .                                             | 264        | 12.2.5    | Calculation Rate . . . . .                                       | 303        |

| 11.2.1    | Introduction . . . . .                                    | 264        | 12.2.6    | CRC Configuration Process . . . . .                              | 303        |

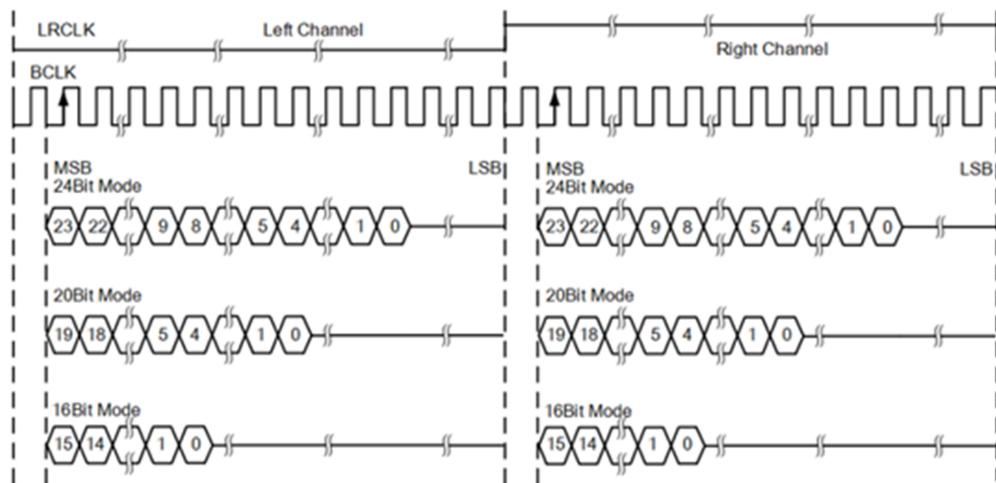

| 11.2.2    | I2S Function Description . . . . .                        | 266        | 12.2.7    | CRC Register . . . . .                                           | 303        |

| 11.2.3    | I2S Register . . . . .                                    | 266        | <b>13</b> | <b>Security</b>                                                  | <b>305</b> |

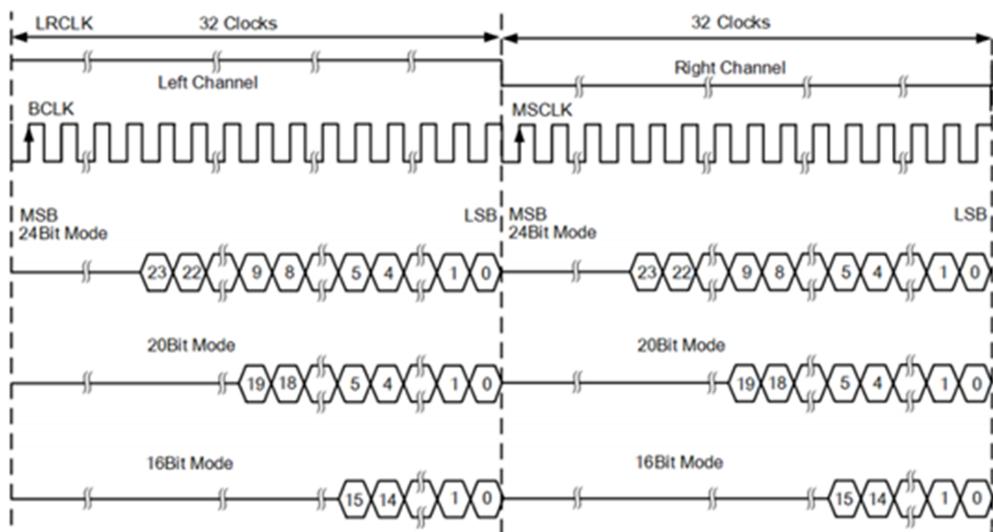

| 11.3      | Audprc . . . . .                                          | 274        | 13.1      | AES . . . . .                                                    | 305        |

| 11.3.1    | Introduction . . . . .                                    | 274        | 13.1.1    | Introduction . . . . .                                           | 305        |

| 11.3.2    | System Architecture . . . . .                             | 274        | 13.1.2    | AES Function Description . . . . .                               | 305        |

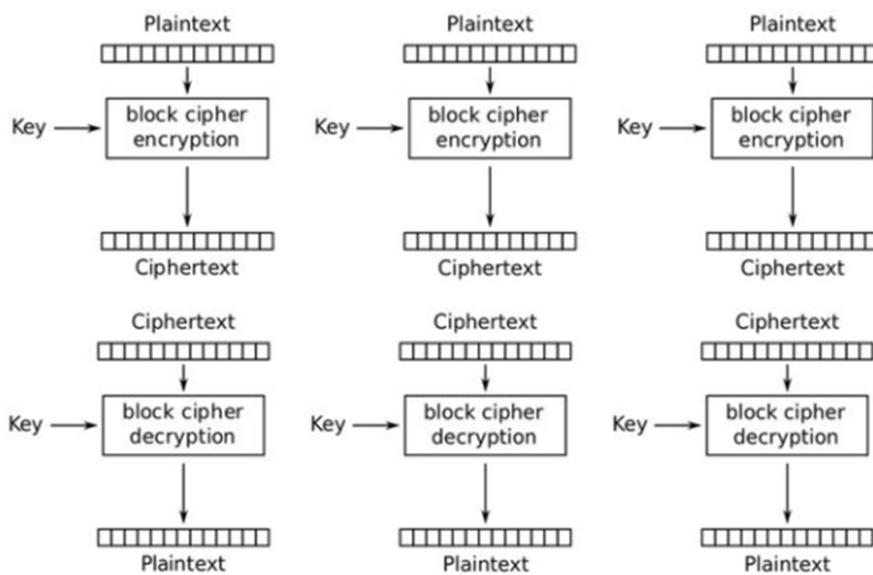

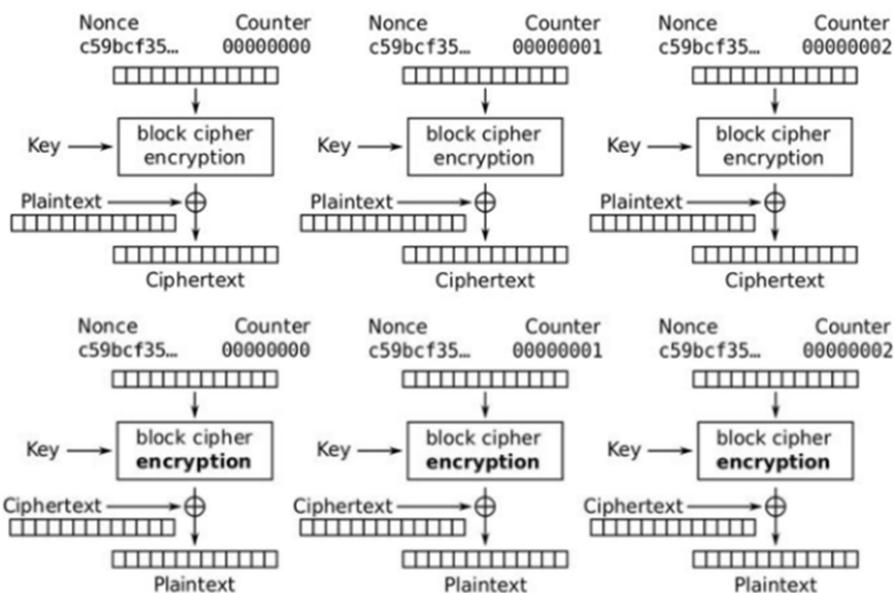

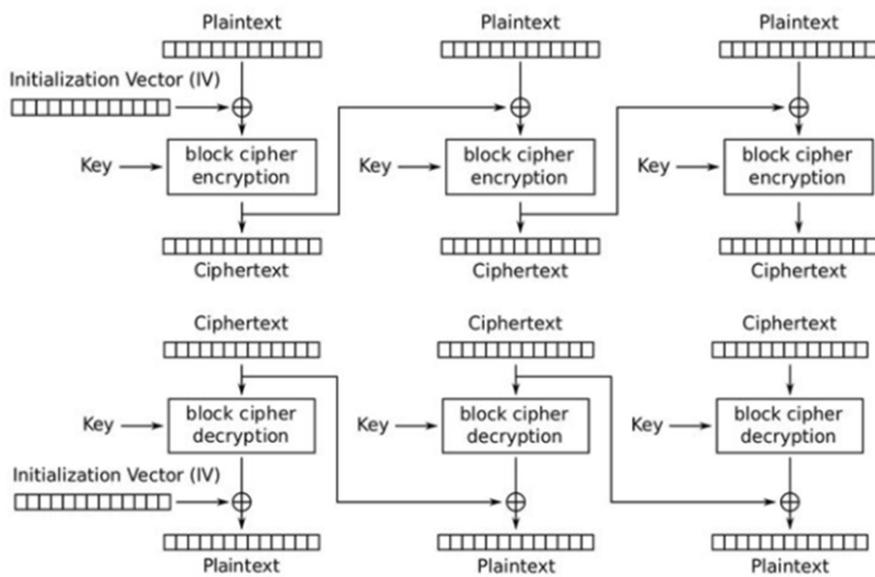

| 11.3.3    | Function Description . . . . .                            | 275        | 13.1.2.1  | Symmetric Encryption Algorithm . . . . .                         | 305        |

| 11.3.3.1  | Sample Rate Conversion Module . . . . .                   | 275        | 13.1.2.2  | Symmetric Encryption Mode . . . . .                              | 305        |

| 11.3.3.2  | Mixing Module . . . . .                                   | 276        | 13.1.2.3  | Multiple Calls for Symmetric Encryption and Decryption . . . . . | 307        |

| 11.3.3.3  | Gain Adjustment Module . . . . .                          | 276        | 13.1.2.4  | Hash Algorithm . . . . .                                         | 308        |

| 11.3.3.4  | Equalizer Module . . . . .                                | 276        | 13.1.2.5  | Multiple Calls for Hash Value Calculation . . . . .              | 308        |

| 11.3.4    | Configuration Process . . . . .                           | 276        | 13.1.3    | AES Register . . . . .                                           | 308        |

| 11.3.4.1  | Configuration of Tx and Rx Channels . . . . .             | 276        | 13.2      | TRNG . . . . .                                                   | 311        |

| 11.3.4.2  | Configuring the DAC Path . . . . .                        | 277        |           |                                                                  |            |

| 11.3.4.3  | Configuring the ADC Path . . . . .                        | 277        |           |                                                                  |            |

|           |                                 |            |           |                                                                            |            |

|-----------|---------------------------------|------------|-----------|----------------------------------------------------------------------------|------------|

| 13.2.1    | Introduction                    | 311        | 15.3      | Debugging Method                                                           | 341        |

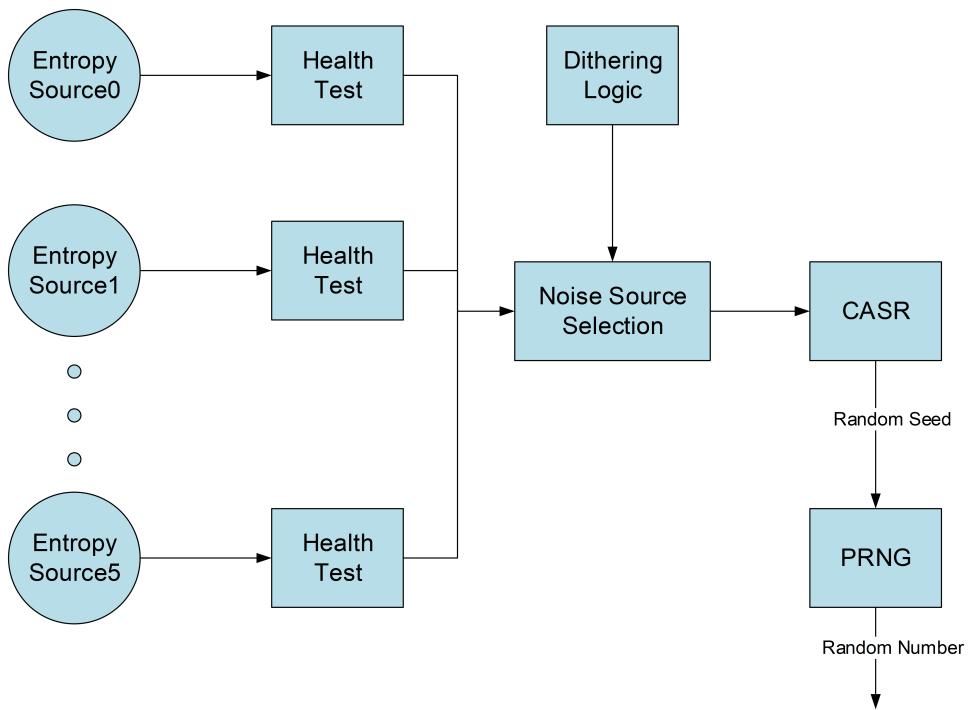

| 13.2.2    | Module Architecture             | 312        | 15.4      | Custom Debug Frame                                                         | 342        |

| 13.2.3    | Function Description            | 312        | 15.5      | Debugging Example                                                          | 343        |

| 13.2.3.1  | Entropy Source                  | 312        | 15.6      | Address Mapping                                                            | 343        |

| 13.2.3.2  | Random Seed Generator           | 312        | 15.7      | HCPU Debugging                                                             | 344        |

| 13.2.3.3  | Random Number Generator         | 313        | 15.8      | USART1 Behavior                                                            | 344        |

| 13.2.3.4  | Other Functional Modules        | 313        | 15.9      | Debug Interface Failure                                                    | 344        |

| 13.2.4    | TRNG Register                   | 313        | 15.10     | Coexistence of debug data and normal data                                  | 345        |

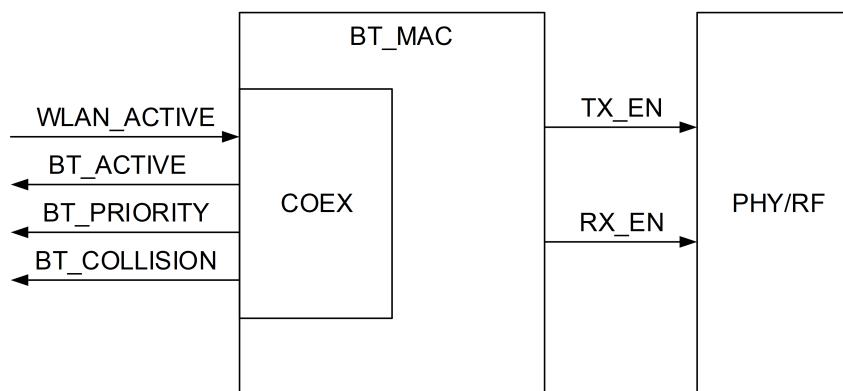

| 13.3      | efusec                          | 315        | <b>16</b> | <b>BlueTooth</b>                                                           | <b>346</b> |

| 13.3.1    | Introduction                    | 315        | 16.1      | Introduction                                                               | 346        |

| 13.3.2    | Main Features                   | 315        | 16.2      | Bluetooth Coexistence Interface                                            | 346        |

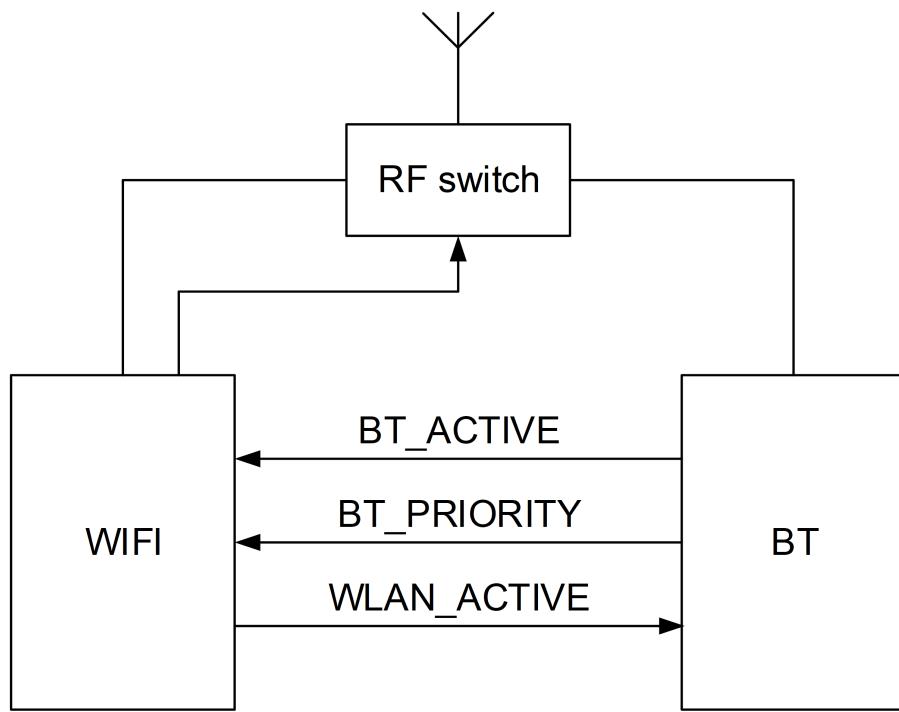

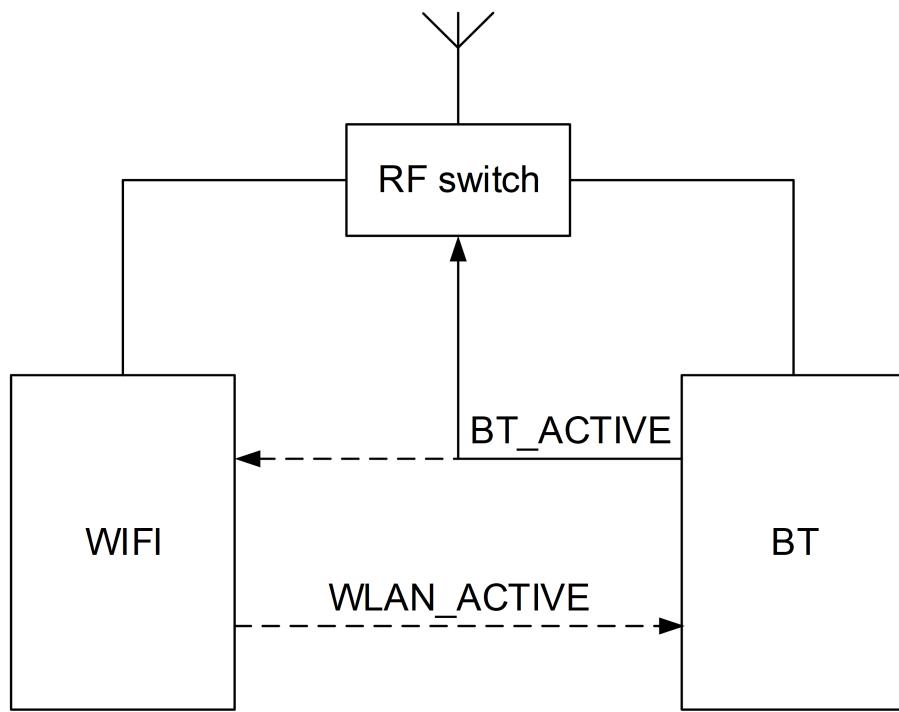

| 13.3.3    | Write Operation                 | 315        | 16.2.1    | Introduction                                                               | 347        |

| 13.3.4    | Read Operation                  | 316        | 16.2.2    | Main Features                                                              | 347        |

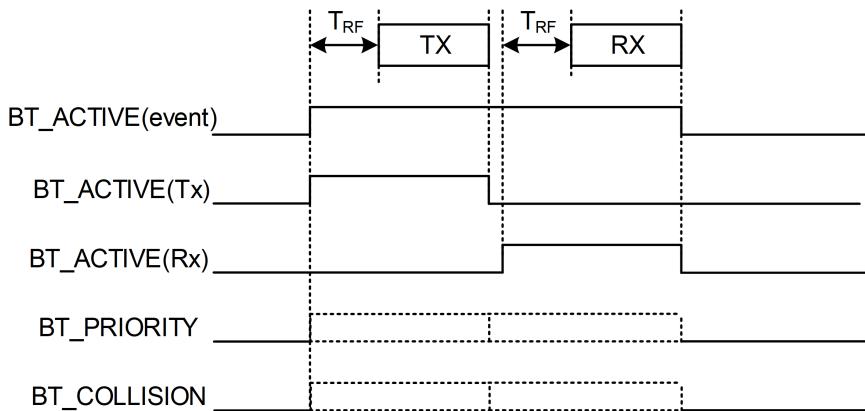

| 13.3.4.1  | Read and Write Timing Control   | 316        | 16.2.3    | Output Signal BT_ACTIVE                                                    | 347        |

| 13.3.4.2  | Read/Write Masking Function     | 316        | 16.2.4    | Output Signal BT_PRIORITY                                                  | 348        |

| 13.3.4.3  | Module Interface Output Signals | 316        | 16.2.5    | Output Signal BT_COLLISION                                                 | 348        |

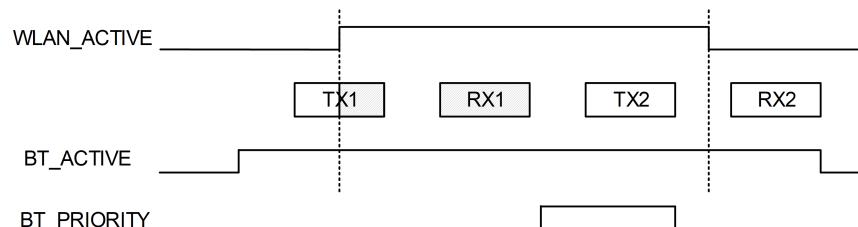

| 13.3.5    | efusec Register                 | 317        | 16.2.6    | Input Signal WLAN_ACTIVE                                                   | 349        |

| <b>14</b> | <b>Storage Interface</b>        | <b>320</b> | 16.2.7    | Procedure for Configuring the Co-existence Interface                       | 349        |

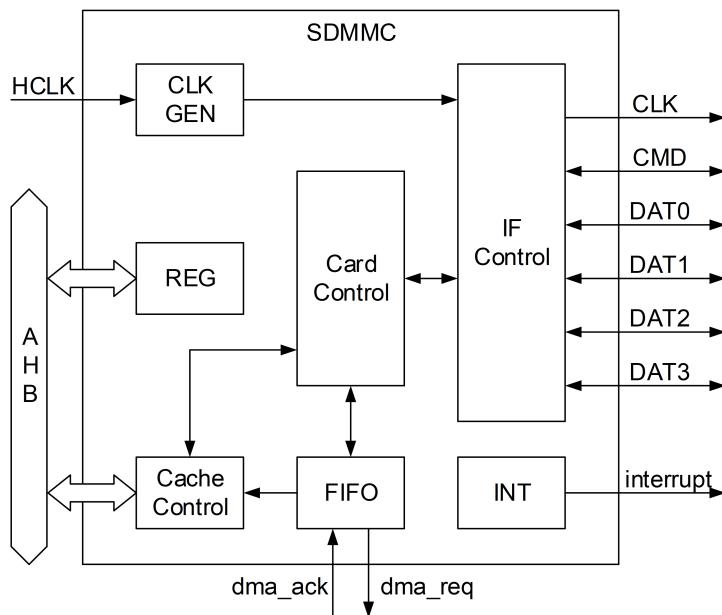

| 14.1      | SD/SDIO/eMMC                    | 320        | 16.2.8    | IO Mapping                                                                 | 350        |

| 14.1.1    | Introduction                    | 320        | 16.2.9    | Example of a 3-wire external arbitration scheme                            | 350        |

| 14.1.2    | Main Features                   | 320        | 16.2.10   | Example of a single-wire internal arbitration scheme                       | 351        |

| 14.1.3    | Function Description            | 321        | 16.3      | Externally connecting a PA (Power Amplifier) and LNA (Low Noise Amplifier) | 352        |

| 14.1.3.1  | SD/eMMC Interface               | 321        |           |                                                                            |            |

| 14.1.3.2  | Clock Settings                  | 321        |           |                                                                            |            |

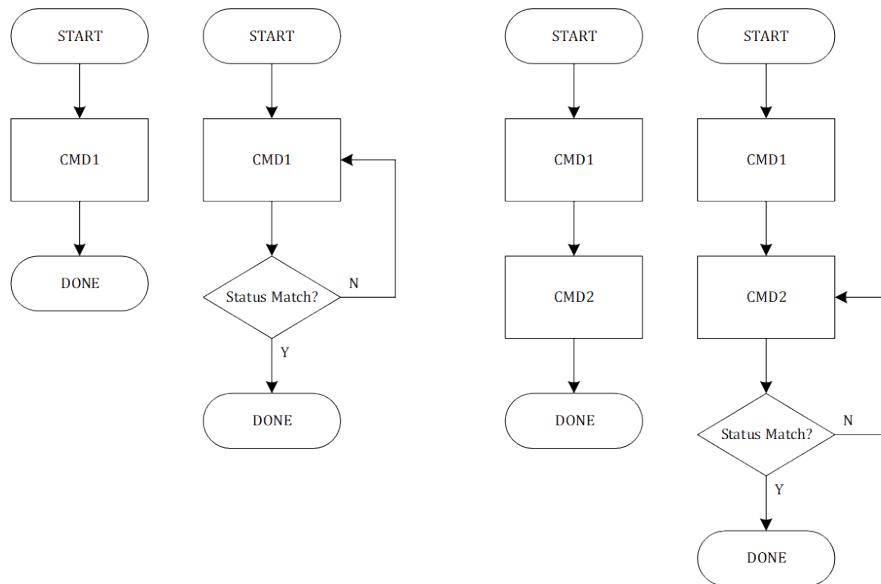

| 14.1.3.3  | Sending Commands                | 321        |           |                                                                            |            |

| 14.1.3.4  | Data Transmission               | 323        |           |                                                                            |            |

| 14.1.3.5  | Interrupt Generation            | 324        |           |                                                                            |            |

| 14.1.3.6  | FIFO Management                 | 324        |           |                                                                            |            |

| 14.1.3.7  | eMMC Open Drain Mode            | 324        |           |                                                                            |            |

| 14.1.3.8  | SDIO Interrupt                  | 325        |           |                                                                            |            |

| 14.1.3.9  | Card Detection                  | 325        |           |                                                                            |            |

| 14.1.3.10 | Bus Direct Read Mode            | 325        |           |                                                                            |            |

| 14.1.3.11 | Sampling Clock Adjustment       | 326        |           |                                                                            |            |

| 14.1.4    | SDMMC Register                  | 326        |           |                                                                            |            |

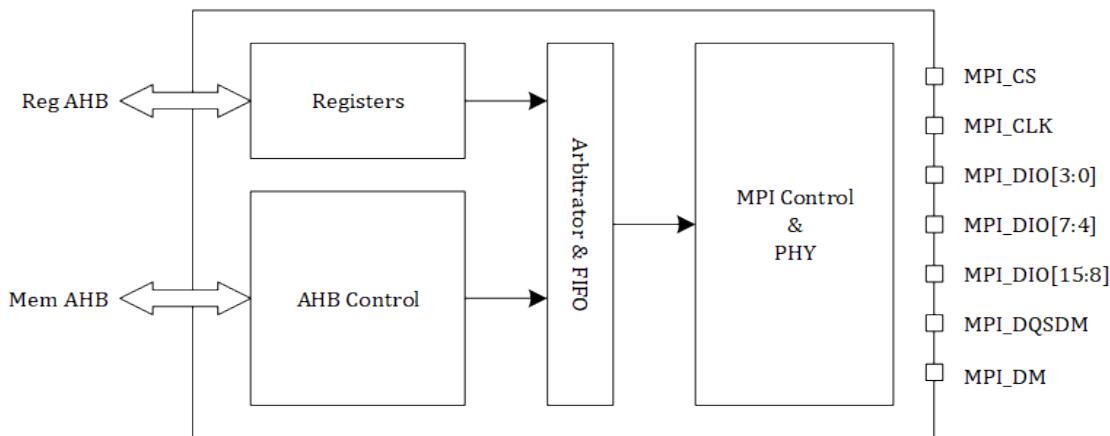

| 14.2      | MPI                             | 332        |           |                                                                            |            |

| 14.2.1    | MPI Register                    | 333        |           |                                                                            |            |

| <b>15</b> | <b>Debug Interface</b>          | <b>341</b> |           |                                                                            |            |

| 15.1      | Introduction                    | 341        |           |                                                                            |            |

| 15.2      | Main Features                   | 341        |           |                                                                            |            |

## List of Figures

|                                                                                                                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0-1 Functional Block Diagram . . . . .                                                                                                                                                   | ii  |

| 1-1 Bus Architecture of HPSYS . . . . .                                                                                                                                                  | 2   |

| 2-1 HPSYS Clock Structure . . . . .                                                                                                                                                      | 11  |

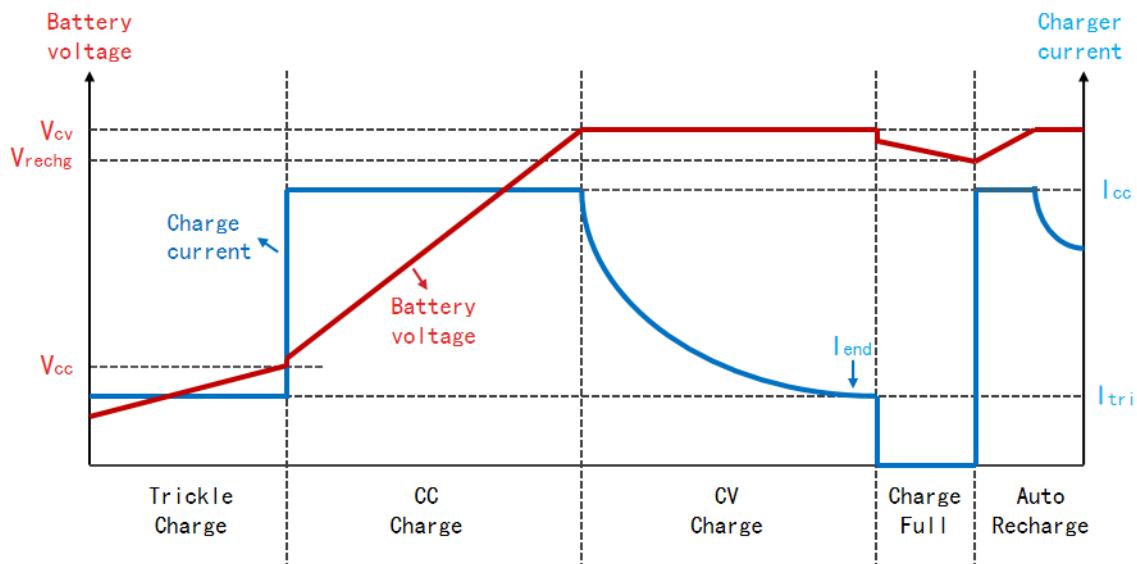

| 3-1 52x Power Management Architecture . .                                                                                                                                                | 25  |

| 3-2 52X Power Management Architecture . .                                                                                                                                                | 28  |

| 3-3 Charging Curve . . . . .                                                                                                                                                             | 31  |

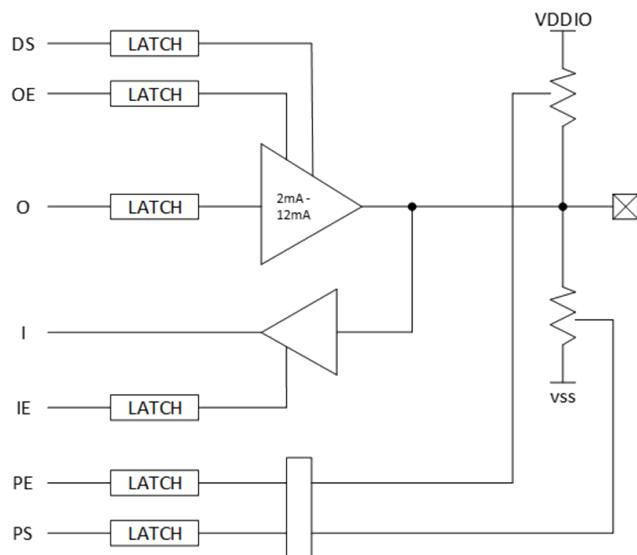

| 5-1 IO Structure . . . . .                                                                                                                                                               | 48  |

| 6-1 DMAC Block Diagram . . . . .                                                                                                                                                         | 87  |

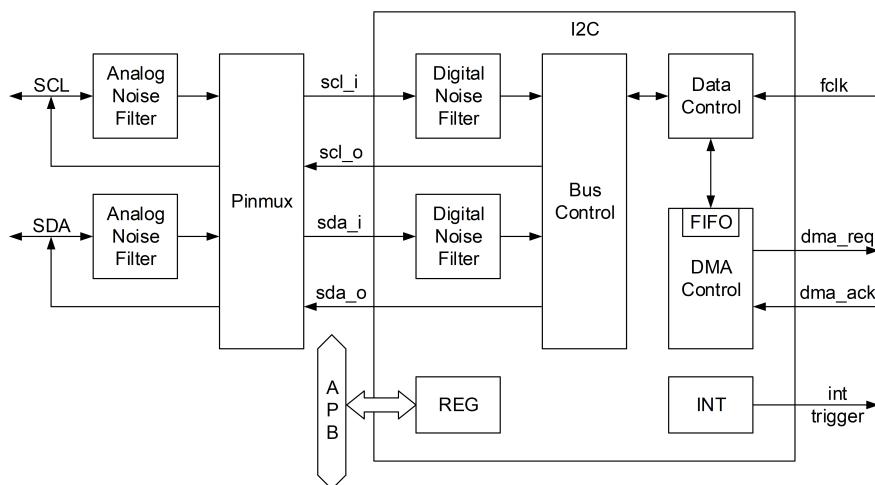

| 7-1 I2C Schematic Diagram . . . . .                                                                                                                                                      | 117 |

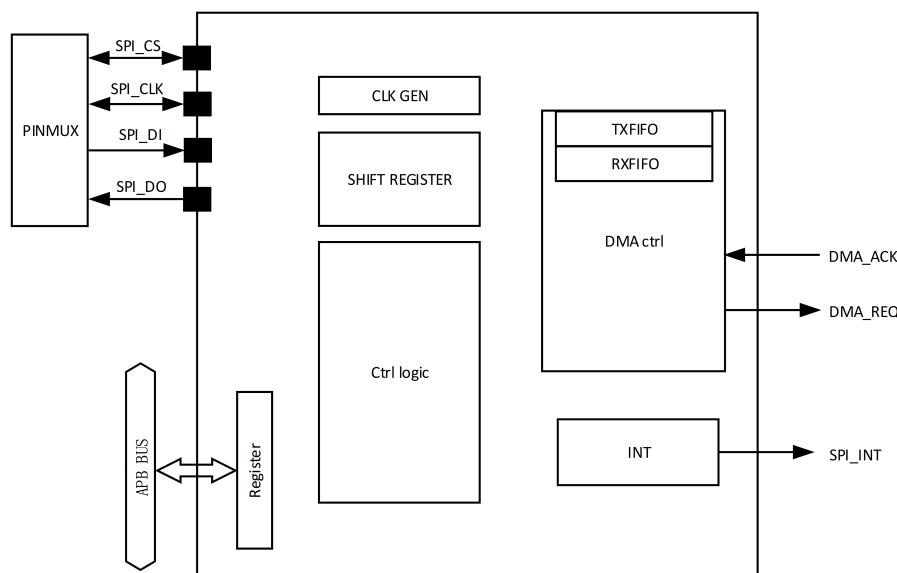

| 7-2 SPI Block Diagram . . . . .                                                                                                                                                          | 127 |

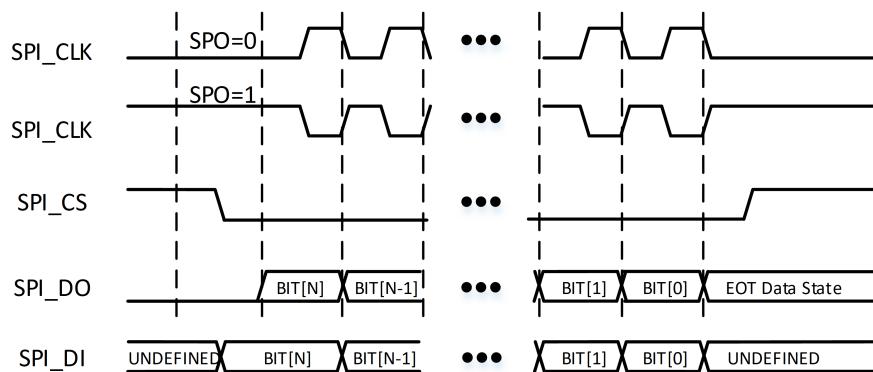

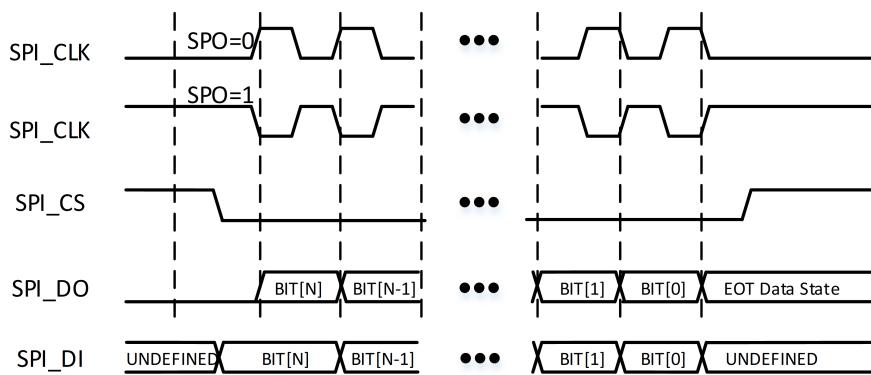

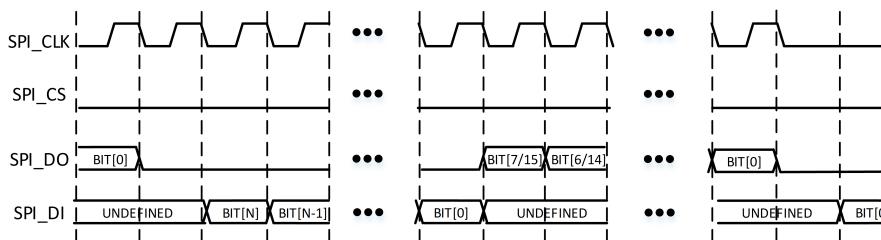

| 7-3 SPI communication when SPH is 0 . . .                                                                                                                                                | 130 |

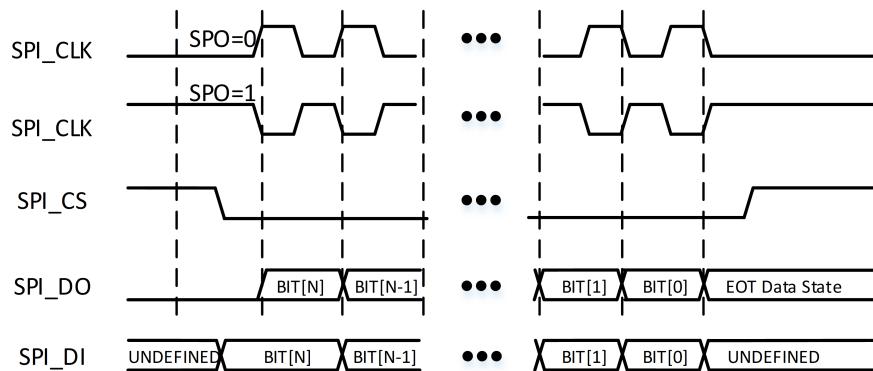

| 7-4 SPI communication when SPH is 1 . . .                                                                                                                                                | 130 |

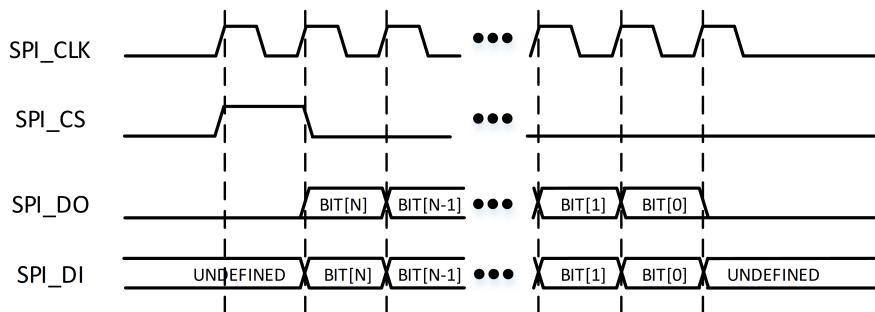

| 7-5 SPI Protocol Continuous Transmission Timing . . . . .                                                                                                                                | 131 |

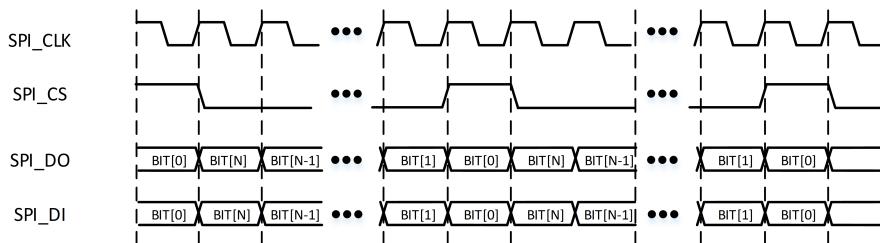

| 7-6 TI-SSP Protocol Communication Timing .                                                                                                                                               | 132 |

| 7-7 TI-SSP Protocol Continuous Communication Timing . . . . .                                                                                                                            | 132 |

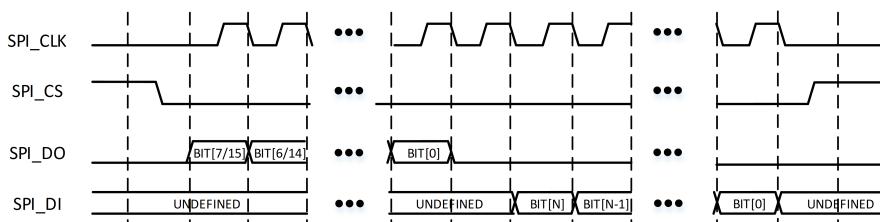

| 7-8 Microwire Protocol Single Communication Timing . . . . .                                                                                                                             | 132 |

| 7-9 Microwire Protocol Continuous Transmission Timing . . . . .                                                                                                                          | 133 |

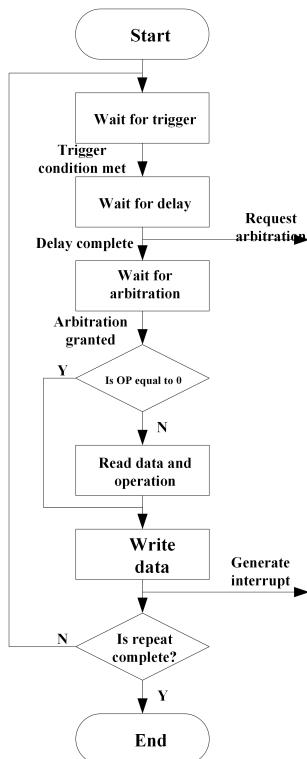

| 7-10 PTC Channel Execution Flowchart . . . .                                                                                                                                             | 142 |

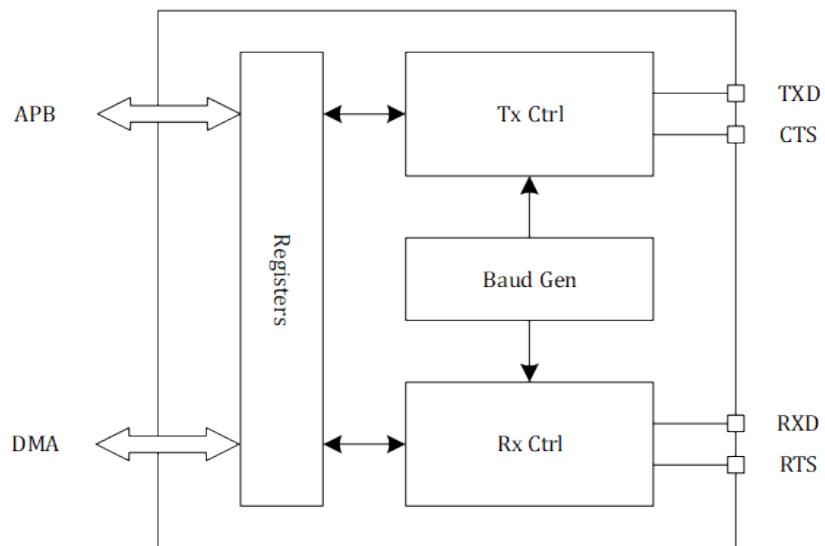

| 7-11 Universal Asynchronous Transceiver . .                                                                                                                                              | 151 |

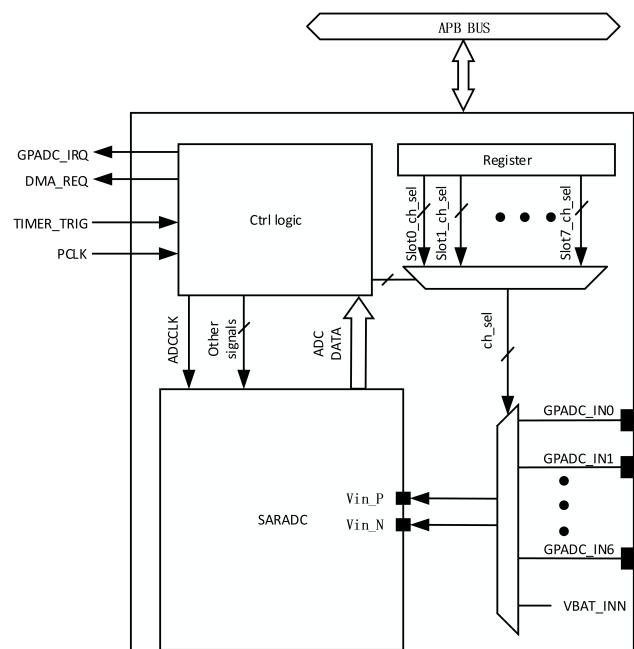

| 8-1 Block Diagram . . . . .                                                                                                                                                              | 157 |

| 9-1 ATIM Structure Diagram . . . . .                                                                                                                                                     | 167 |

| 9-2 PWM output in increment counting mode                                                                                                                                                | 172 |

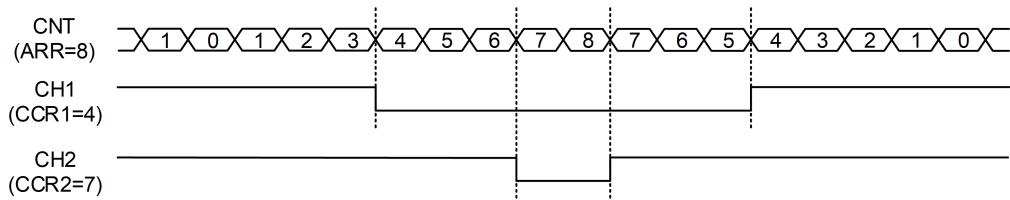

| 9-3 PWM output in center-aligned counting mode . . . . .                                                                                                                                 | 172 |

| 9-4 Asymmetric PWM Output . . . . .                                                                                                                                                      | 173 |

| 9-5 Combined PWM Output . . . . .                                                                                                                                                        | 173 |

| 9-6 Complementary PWM output with dead time . . . . .                                                                                                                                    | 174 |

| 9-7 BTIM Block Diagram . . . . .                                                                                                                                                         | 197 |

| 9-8 GPTIM Block Diagram . . . . .                                                                                                                                                        | 204 |

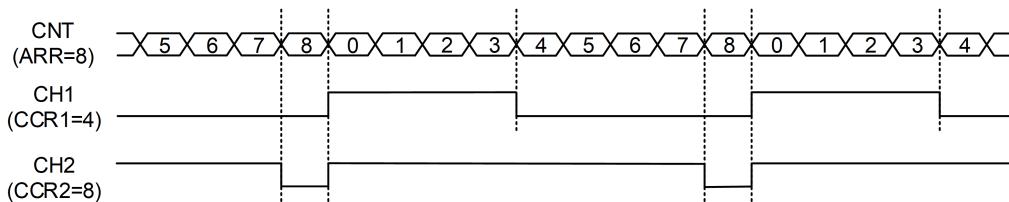

| 9-9 PWM output in increment counting mode                                                                                                                                                | 208 |

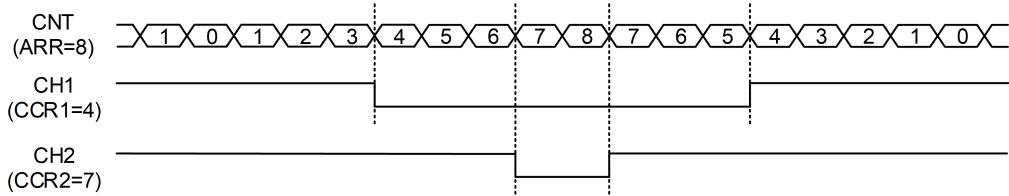

| 9-10 PWM output in center-aligned counting mode . . . . .                                                                                                                                | 209 |

| 9-11 Asymmetric PWMO utput . . . . .                                                                                                                                                     | 209 |

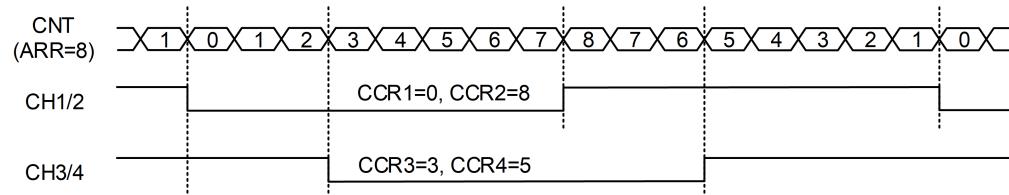

| 9-12 Combined PWM Output . . . . .                                                                                                                                                       | 210 |

| 9-13 LPTIM structure diagram . . . . .                                                                                                                                                   | 226 |

| 9-14 PWM Output . . . . .                                                                                                                                                                | 228 |

| 9-15 The relationship between the interrupt and resetsignal generation in Mode 1 and the counter (assuming a timeout value of 20, withresetactive low) . . . . .                         | 234 |

| 9-16 The relationship between the interrupt and resetsignal generation in Mode 2 and the counter (assuming a timeout value of 20, withresetactive low). . . . .                          | 234 |

| 9-17 Mode 1 The effect of the 'dog feeding' action on the counter (assuming the timeout value is 20) . . . . .                                                                           | 234 |

| 9-18 Mode 2 The effect of the 'dog feeding' operation on the counter during the second round of counting is the same as in the first round (assuming the timeout value is 20 ) . . . . . | 234 |

| 10-1 LCDC Architecture Diagram . . . . .                                                                                                                                                 | 243 |

| 11-1 Typical connection of a digital microphone through the PDM Module . . . . .                                                                                                         | 258 |

| 11-2 Overall Structure of the PDM Module . .                                                                                                                                             | 259 |

| 11-3 Clock Structure of the PDM Module . .                                                                                                                                               | 259 |

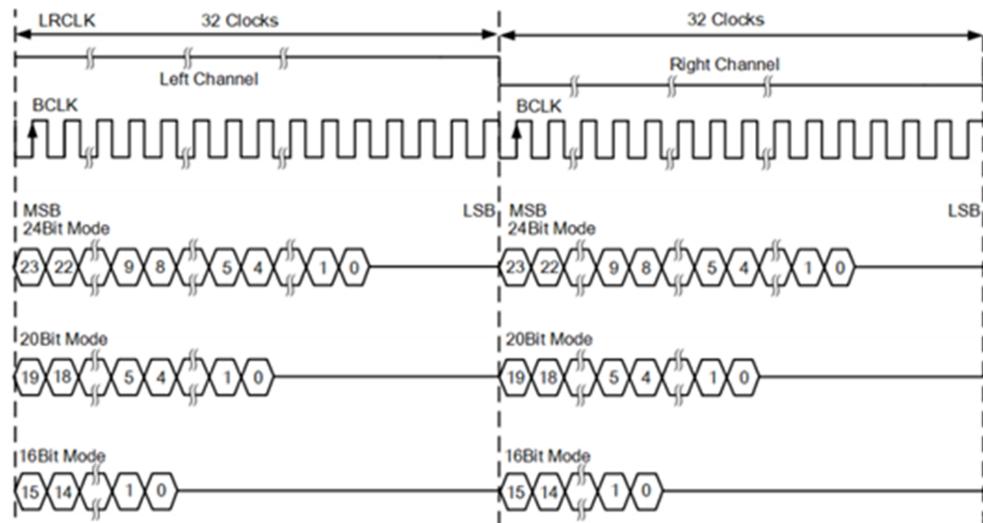

| 11-4 Standard I2S Mode . . . . .                                                                                                                                                         | 265 |

| 11-5 I2S Left Alignment . . . . .                                                                                                                                                        | 265 |

| 11-6 I2S Right Alignment . . . . .                                                                                                                                                       | 266 |

| 11-7 Audprc Block Diagram . . . . .                                                                                                                                                      | 275 |

| 11-8 Audcodec Path Structure . . . . .                                                                                                                                                   | 288 |

| 13-1 ECB Mode Decryption . . . . .                                                                                                                                                       | 306 |

| 13-2 CTR Mode Decryption . . . . .                                                                                                                                                       | 306 |

| 13-3 CBC Mode Decryption . . . . .                                                                                                                                                       | 307 |

| 13-4 TRNG Schematic Diagram . . . . .                                                                                                                                                    | 312 |

| 14-1 SDMMC Block Diagram . . . . .                                                                                                                                                       | 321 |

| 14-2 MPI Controller Block Diagram . . . . .                                                                                                                                              | 332 |

| 14-3 Register mode for single and multiple command timing sequences . . . . .                                                                                                            | 333 |

| 16-1 Bluetooth Coexistence Diagram . . . . .                                                                                                                                             | 347 |

| 16-2 Output Signal Diagram . . . . .                                                                                                                                                     | 348 |

| 16-3 Example of WLAN_ACTIVE impact . . . .                                                                                                                                               | 349 |

| 16-4 Example of a 3-wire external arbitration scheme . . . . .                                                                                                                           | 351 |

| 16-5 Examples of internal arbitration single-wire or 2-wire schemes . . . . .                                                                                                            | 352 |

## List of Tables

|     |                                                                     |     |

|-----|---------------------------------------------------------------------|-----|

| 1-1 | Address Mapping of HPSYS . . . . .                                  | 3   |

| 1-2 | HCPU Interrupt List . . . . .                                       | 5   |

| 1-3 | Bus Access Permissions . . . . .                                    | 6   |

| 2-1 | Main Reset Sources of the Chip . . . . .                            | 9   |

| 2-2 | Main Reset Sources of the Chip-Continued . . . . .                  | 9   |

| 2-3 | Clock Source . . . . .                                              | 10  |

| 2-4 | clk_rtc related module operational clock . . . . .                  | 12  |

| 2-5 | clk_wdt Related module operating clock . . . . .                    | 12  |

| 2-6 | HPSYS_RCC Register Mapping Table . . . . .                          | 17  |

| 3-1 | power pin for 52x lithium battery-powered version . . . . .         | 27  |

| 3-2 | Power Pin for SF32LB52X Conventional Power Supply Version . . . . . | 30  |

| 3-3 | PMUC Register Mapping Table . . . . .                               | 31  |

| 4-1 | Chip Operating Modes . . . . .                                      | 39  |

| 4-2 | Power Pin Voltage in Low Power Mode . . . . .                       | 44  |

| 4-3 | HPSYS_AON Register Mapping Table . . . . .                          | 44  |

| 5-1 | Big Core Domain (PA) PIN Function List . . . . .                    | 51  |

| 5-2 | IO Working Status . . . . .                                         | 60  |

| 5-3 | IO Leakage Inspection Table . . . . .                               | 61  |

| 5-4 | HPSYS_PINMUX Register Mapping Table . . . . .                       | 62  |

| 5-5 | HPSYS_CFG Register Mapping Table . . . . .                          | 75  |

| 5-6 | HPSYS_GPIO Register Mapping Table . . . . .                         | 82  |

| 6-1 | DMAC Peripheral Request Table . . . . .                             | 86  |

| 6-2 | DMAC Transmission Direction . . . . .                               | 89  |

| 6-3 | DMAC Transmission Bit Width . . . . .                               | 89  |

| 6-4 | DMAC Register Mapping Table . . . . .                               | 92  |

| 6-5 | ExtDMA Register Mapping Table . . . . .                             | 113 |

| 7-1 | I2C Register Mapping Table . . . . .                                | 121 |

| 7-2 | SPI Register Mapping Table . . . . .                                | 136 |

|      |                                                                                              |     |

|------|----------------------------------------------------------------------------------------------|-----|

| 7-3  | PTC1 Trigger Source . . . . .                                                                | 141 |

| 7-4  | PTC Register Mapping Table . . . . .                                                         | 143 |

| 7-5  | USART Register Mapping Table . . . . .                                                       | 152 |

| 8-1  | GPADC Register Mapping Table . . . . .                                                       | 161 |

| 8-2  | TSEN Register Mapping Table . . . . .                                                        | 165 |

| 9-1  | ATIM Register Mapping Table . . . . .                                                        | 177 |

| 9-2  | BTIM Register Mapping Table . . . . .                                                        | 199 |

| 9-3  | GPTIM Register Mapping Table . . . . .                                                       | 212 |

| 9-4  | Timer Cascading . . . . .                                                                    | 224 |

| 9-5  | LPTIM Register Mapping Table . . . . .                                                       | 228 |

| 9-6  | WDT Register Mapping Table . . . . .                                                         | 235 |

| 9-7  | RTC Register Mapping Table . . . . .                                                         | 236 |

| 10-1 | LCDC Register Mapping Table . . . . .                                                        | 246 |

| 11-1 | PDM Microphone Clock Source and Corresponding Output Data Rate Configuration Table . . . . . | 259 |

| 11-2 | PDM Register Mapping Table . . . . .                                                         | 263 |

| 11-3 | I2S Register Mapping Table . . . . .                                                         | 266 |

| 11-4 | Audprc Register Mapping Table . . . . .                                                      | 277 |

| 11-5 | Audcodec Register Map . . . . .                                                              | 289 |

| 12-1 | CRC Configuration Method . . . . .                                                           | 302 |

| 12-2 | Data Participating in the Calculation . . . . .                                              | 302 |

| 12-3 | Operation Sequence . . . . .                                                                 | 303 |

| 12-4 | CRC Register Mapping Table . . . . .                                                         | 303 |

| 13-1 | AES Register Mapping Table . . . . .                                                         | 308 |

| 13-2 | TRNG Register Mapping Table . . . . .                                                        | 313 |

| 13-3 | efuse interface signals . . . . .                                                            | 317 |

| 13-4 | efusec Register Mapping Table . . . . .                                                      | 317 |

| 14-1 | SDMMC Register Mapping Table . . . . .                                                       | 326 |

| 14-2 | MPI Register Mapping Table . . . . .                                                         | 333 |

| 15-1 | Custom Debug Frame Format . . . . .                                                          | 342 |

| 15-2 | UART Debug Interface Address Mapping . . . . .                                               | 344 |

# 1 Introduction

## 1.1 System Architecture

SF32LB52x is a family of highly integrated high-performance MCUs designed for ultra-low-power Artificial Intelligence of Things (AIoT) scenarios. SF32LB52x adopts the big.LITTLE architecture with the Arm Cortex-M33 STAR-MC1 processor.

- High-Performance Processor/Big Core (HCPU): 32KB instruction cache (I-Cache) and 16KB data cache (D-Cache), 512KB SRAM (All Retention SRAM); Up to 240MHz clock frequency, it can dynamically switch between basic-working mode and enhance-working mode for efficient access to on-chip and off-chip memory. As the system master, enhance-working mode is mainly used for system control, Human-Machine Interaction, and high-performance computing; Meanwhile, as the low-power sensor hub, basic-working mode can be used for all kinds of data acquisition and processing in low-power scenarios.

- Ultra-low Power Processor/LITTLE Core (LCPU): Up to 24MHz clock frequency, 64KB SRAM (all Retention SRAM); it is mainly used for transmission control and basic data processing of Bluetooth Low Energy.

## 1.2 Cortex-M33 STAR-MC1 Processor

Cortex-M33 STAR-MC1 processor is the first processor of the "Star" series from Arm China. It has the key features of Cortex-M33, supporting the full functionality of the existing Arm v8-M architecture, and with an in-order three-stage pipeline, it can significantly reduce the power consumption of the system. It also has partial dual-issue 16-bit instruction capability, the coprocessor interface is further improved and support the Cache.

With the performance reaching 1.5DMIPS/MHz and 4.02Coremark/MHz, Cortex-M33 STAR-MC1 delivers a 20% performance improvement over previous-generation Arm processors at the same clock speed.

Cortex-M33 STAR-MC1 has a coprocessor interface which can further enhance the capability of customized calculation to meet the requirements of different scenarios. The MCR (Move from Coprocessor to Register) and MRC (Move from Register to Coprocessor) instructions enable the transfer of register data and computation results between Cortex-M33 STAR-MC1 and the coprocessor, making it ideal for operations with small data volumes, complex calculations but relatively fragmented and low latency. While the coprocessor computes, Cortex-M33 STAR-MC1 processor can still execute other instructions in parallel, thus significantly improving execution efficiency.

In addition, the processor supports Digital Signal Processing (DSP) instruction sets and Floating Point Unit (FPU).

Tightly Coupled Memory (TCM) and Cache technologies are adopted in Cortex-M33 STAR-MC1 processor to enhance flexibility in the use of internal and external memory systems with different characteristics, ensuring the real-time response and computational efficiency of the processor in a variety of scenarios.

## 1.3 High-Performance Processor (Big Core) System (HPSYS)

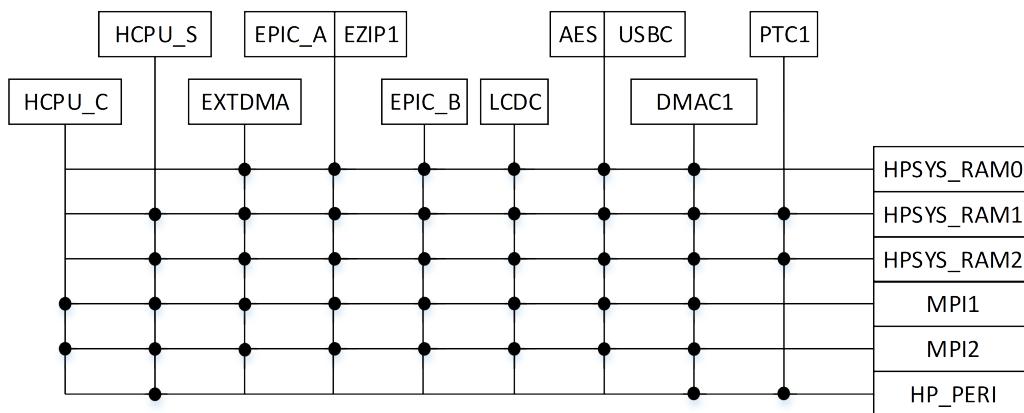

### 1.3.1 Bus Architecture

The HPSYS provides an internal bus matrix based on the AHB protocol, which supports multiple master devices to access the address spaces of multiple slave devices in parallel.

As shown in Figure 1-1, the master devices of the bus are located on the top side and the address spaces of the slave devices are located on the right side, and the black dots at the intersection represent bus connectivity.

The HCPU and DMAC1 has access to all address spaces of the HPSYS.

128KB address space is shared between DTCM and HPSYS\_RAM0, and can be accessed by the HCPU and other master devices.

HP\_PERI includes APB-related peripherals and AHB-related peripherals, and can be accessed by HCPU, DMAC1 and PTC1.

When multiple master devices access the address space of the same slave device at the same time, the access order will be determined based on the Round-Robin Arbitration Principle.

As shown in the figure, when multiple master devices with unconnected borders access the address spaces of different slave devices at the same time, they will not be affected by each other. When two master devices with connected borders initiate access at the same time, the access order will be decided based on the Round-Robin Arbitration Principle.

Figure 1-1: Bus Architecture of HPSYS

### 1.3.2 Memory Type

#### 1.3.2.1 Cache

The HCPU has 32KB 2-way I-Cache (Level 1 instruction cache) and 16KB 4-way D-Cache (Level 1 data cache), which can greatly improve CPU execution efficiency during XIP. The MPU (Memory Protection Unit) should be configured appropriately to set the cache address segment and non-cache address segment to balance efficiency and ease of use.

#### 1.3.2.2 TCM

The HCPU has 128KB zero-wait-cycle D-TCM with address space 0x2000\_0000-0x2001\_FFFF, which can be used to place codes and data with high real-time requirements. This TCM memory is connected to the bus and can be accessed by

other AHB masters.

### 1.3.2.3 SRAM

There is a total of 512KB SRAM on the HPSYS bus, which includes:

- 0x2000\_0000-0x2001\_FFFF, 128KB zero-wait-cycle SRAM (shared with D-TCM), accessible to all AHB masters. Maximum frequency is 240MHz.

- 0x2002\_0000-0x2007\_FFFF, 384KB zero-wait-cycle SRAM, accessible to all AHB masters. Maximum frequency is 240MHz.

### 1.3.2.4 Off-chip RAM

The HPSYS supports combined 4-wire and 8-wire pSRAM with address space 0x6000\_0000 - 0x61FF\_FFFF, the actual accessible address is determined by the capacity of the external particles. The maximum interface frequency is DDR 144MHz and the data bit width is 8-bit.

### 1.3.2.5 Off-chip Flash

The HPSYS supports external NOR/NAND FLASHs, in which

- 0x6000\_0000-0x61FF\_FFFF address segment can be combined with FLASH, recommended frequency is 96MHz

- 0x6200\_0000-0x9FFF\_FFFF address segment can be connected to external FLASH, recommended frequency is 60MHz

## 1.3.3 Address Mapping

**Table 1-1: Address Mapping of HPSYS**

| Category        | Memory /IP  | Address Space | HCPU             |                | LCPU             |                |

|-----------------|-------------|---------------|------------------|----------------|------------------|----------------|

|                 |             |               | Starting Address | Ending Address | Starting Address | Ending Address |

| HPSYS_ITCM      |             | 64KB          | 0x0000_0000      | 0x0000_FFFF    | NA               | NA             |

|                 | ROM         | 64KB          | 0x0000_0000      | 0x0000_FFFF    | -                | -              |

|                 | Reserved    | -             | -                | -              | -                | -              |

| External Memory |             | 1024MB        | *0x1000_0000     | 0x6000_0000    | *0x1FFF_FFFF     | 0x6000_0000    |

|                 | MP11 Memory | 32MB          | *0x1000_0000     | 0x6000_0000    | *0x1FFF_FFFF     | 0x6000_0000    |

|                 | MP12 Memory | 224MB/92MB    | *0x1200_0000     | 0x6200_0000    | *0x1FFF_FFFF     | 0x6200_0000    |

| HPSYS_RAM       |             | 512KB         | 0x2000_0000      | -              | 0x2007_FFFF      | 0x2A00_0000    |

|                 | RAM0 (DTCM) | 128KB         | 0x2000_0000      | -              | 0x2001_FFFF      | 0x2A00_0000    |

|                 | RAM1        | 128KB         | 0x2002_0000      | -              | 0x2003_FFFF      | 0x2A02_0000    |

|                 | RAM2        | 256KB         | 0x2004_0000      | -              | 0x2007_FFFF      | 0x2A04_0000    |

| HPSYS_APB1      |             | 256KB         | 0x5000_0000      | -              | 0x5003_FFFF      | 0x5000_0000    |

|                 | RCC1        | 4KB           | 0x5000_0000      | -              | 0x5000_0FFF      | 0x5000_0000    |

|                 | EXTDMA      | 4KB           | 0x5000_1000      | -              | 0x5000_1FFF      | 0x5000_1000    |

|                 | SECU1       | 4KB           | 0x5000_2000      | -              | 0x5000_2FFF      | 0x5000_2000    |

|                 | PINMUX1     | 4KB           | 0x5000_3000      | -              | 0x5000_3FFF      | 0x5000_3000    |

|                 | ATIM1       | 4KB           | 0x5000_4000      | -              | 0x5000_4FFF      | 0x5000_4000    |

|                 | AUDPRC      | 4KB           | 0x5000_5000      | -              | 0x5000_5FFF      | 0x5000_5000    |

|                 | EZIP1       | 4KB           | 0x5000_6000      | -              | 0x5000_6FFF      | 0x5000_6000    |

|                 | EPIC        | 4KB           | 0x5000_7000      | -              | 0x5000_7FFF      | 0x5000_7000    |

|                 | LCDC1       | 4KB           | 0x5000_8000      | -              | 0x5000_8FFF      | 0x5000_8000    |

|                 | I2S1        | 4KB           | 0x5000_9000      | -              | 0x5000_9FFF      | 0x5000_9000    |

|                 | Reserved    | 4KB           | 0x5000_A000      | -              | 0x5000_AFFF      | 0x5000_A000    |

|                 | SYSCFG1     | 4KB           | 0x5000_B000      | -              | 0x5000_BFFF      | 0x5000_B000    |

|                 | EFUSEC      | 4KB           | 0x5000_C000      | -              | 0x5000_CFFF      | 0x5000_C000    |

|                 | AES         | 4KB           | 0x5000_D000      | -              | 0x5000_DFFF      | 0x5000_D000    |

|                 | Reserved    | 4KB           | 0x5000_E000      | -              | 0x5000_EFFF      | 0x5000_E000    |

|                 | TRNG        | 4KB           | 0x5000_F000      | -              | 0x5000_FFFF      | 0x5000_F000    |

|                 | Reserved    | 4KB           | 0x5001_0000      | -              | 0x5001_0FFF      | 0x5001_0000    |

|                 | Reserved    | 4KB           | 0x5001_1000      | -              | 0x5001_1FFF      | 0x5001_1000    |

|                 | Reserved    | 4KB           | 0x5001_2000      | -              | 0x5001_2FFF      | 0x5001_2000    |

|                 | Reserved    | 4KB           | 0x5001_3000      | -              | 0x5001_3FFF      | 0x5001_3000    |

|                 | Reserved    | 4KB           | 0x5001_4000      | -              | 0x5001_4FFF      | 0x5001_4000    |

|                 | Reserved    | 4KB           | 0x5001_5000      | -              | 0x5001_5FFF      | 0x5001_5000    |

|                 | Reserved    | 4KB           | 0x5001_6000      | -              | 0x5001_6FFF      | 0x5001_6000    |

|                 | Reserved    | 4KB           | 0x5001_7000      | -              | 0x5001_7FFF      | 0x5001_7000    |

Continued on the next page

**Table 1-1: Address Mapping of HPSYS (continued)**

| Category   | Memory /IP       | Address Space | HCPU               |                    | LCPU               |                    |

|------------|------------------|---------------|--------------------|--------------------|--------------------|--------------------|

|            |                  |               | Starting Address   | Ending Address     | Starting Address   | Ending Address     |

| HPSYS_AHB1 | Reserved         | 4KB           | 0x5001_8000        | 0x5001_8FFF        | 0x5001_8000        | 0x5001_8FFF        |

|            | Reserved         | 4KB           | 0x5001_9000        | 0x5001_9FFF        | 0x5001_9000        | 0x5001_9FFF        |

|            | Reserved         | 4KB           | 0x5001_A000        | 0x5001_AFFF        | 0x5001_A000        | 0x5001_AFFF        |

|            | Reserved         | 4KB           | 0x5001_B000        | 0x5001_BFFF        | 0x5001_B000        | 0x5001_BFFF        |

|            | Reserved         | 4KB           | 0x5001_C000        | 0x5001_CFFF        | 0x5001_C000        | 0x5001_CFFF        |

|            | Reserved         | 4KB           | 0x5001_D000        | 0x5001_DFFF        | 0x5001_D000        | 0x5001_DFFF        |

|            | Reserved         | 4KB           | 0x5001_E000        | 0x5001_EFFF        | 0x5001_E000        | 0x5001_EFFF        |

|            | Reserved         | 4KB           | 0x5001_F000        | 0x5001_FFFF        | 0x5001_F000        | 0x5001_FFFF        |

|            | Reserved         | 128KB         | 0x5002_0000        | 0x5003_FFFF        | 0x5002_0000        | 0x5003_FFFF        |

|            | <b>256KB</b>     |               | <b>0x5004_0000</b> | <b>0x5007_FFFF</b> | <b>0x5004_0000</b> | <b>0x5007_FFFF</b> |

| HPSYS_APB2 | Reserved         | 4KB           | 0x5004_0000        | 0x5004_0FFF        | 0x5004_0000        | 0x5004_0FFF        |

|            | <b>MPI1</b>      | <b>4KB</b>    | <b>0x5004_1000</b> | <b>0x5004_1FFF</b> | <b>0x5004_1000</b> | <b>0x5004_1FFF</b> |

|            | <b>MPI2</b>      | <b>4KB</b>    | <b>0x5004_2000</b> | <b>0x5004_2FFF</b> | <b>0x5004_2000</b> | <b>0x5004_2FFF</b> |

|            | Reserved         | 4KB           | 0x5004_3000        | 0x5004_3FFF        | 0x5004_3000        | 0x5004_3FFF        |

|            | Reserved         | 4KB           | 0x5004_4000        | 0x5004_4FFF        | 0x5004_4000        | 0x5004_4FFF        |

|            | <b>SDMMC1</b>    | <b>4KB</b>    | <b>0x5004_5000</b> | <b>0x5004_5FFF</b> | <b>0x5004_5000</b> | <b>0x5004_5FFF</b> |

|            | Reserved         | 4KB           | 0x5004_6000        | 0x5004_6FFF        | 0x5004_6000        | 0x5004_6FFF        |

|            | <b>USBC</b>      | <b>4KB</b>    | <b>0x5004_7000</b> | <b>0x5004_7FFF</b> | <b>0x5004_7000</b> | <b>0x5004_7FFF</b> |

|            | <b>CRC1</b>      | <b>4KB</b>    | <b>0x5004_8000</b> | <b>0x5004_8FFF</b> | <b>0x5004_8000</b> | <b>0x5004_8FFF</b> |

|            | Reserved         | 28KB          | 0x5004_9000        | 0x5004_FFFF        | 0x5004_9000        | 0x5004_FFFF        |

| HPSYS_APB2 | <b>GFX_RAM</b>   | <b>64KB</b>   | <b>0x5005_0000</b> | <b>0x5005_FFFF</b> | <b>0x5005_0000</b> | <b>0x5005_FFFF</b> |

|            | Reserved         | 128KB         | 0x5006_0000        | 0x5007_FFFF        | 0x5006_0000        | 0x5007_FFFF        |

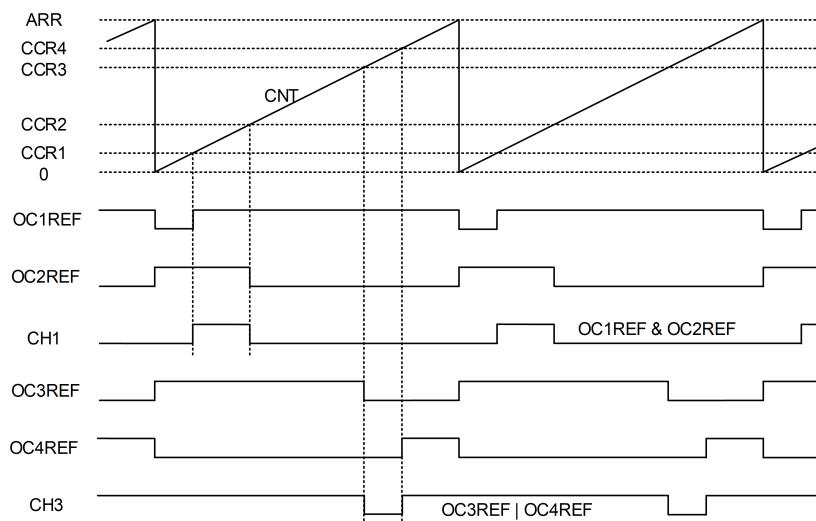

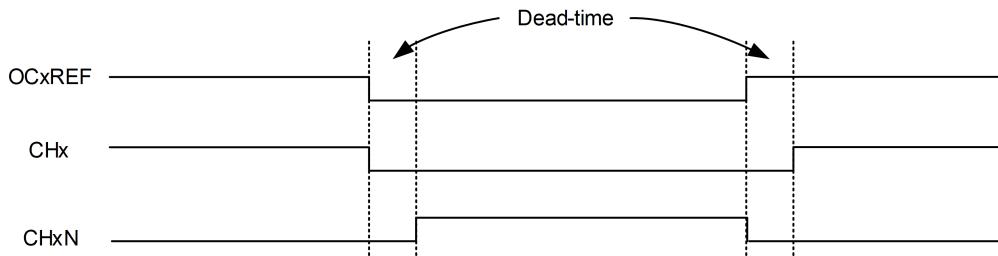

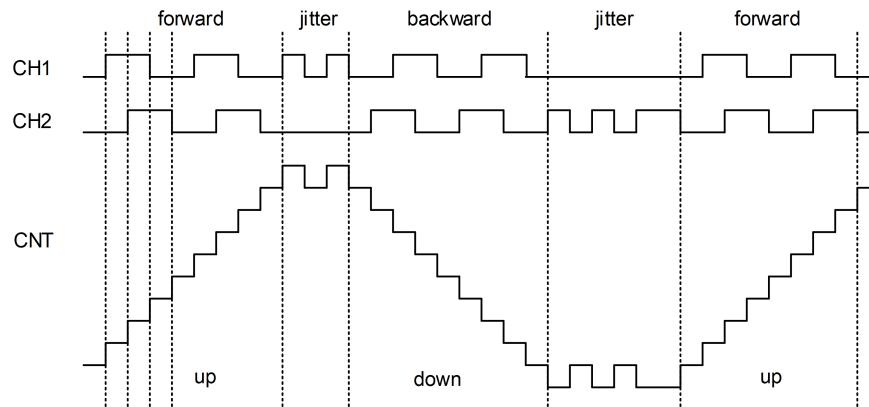

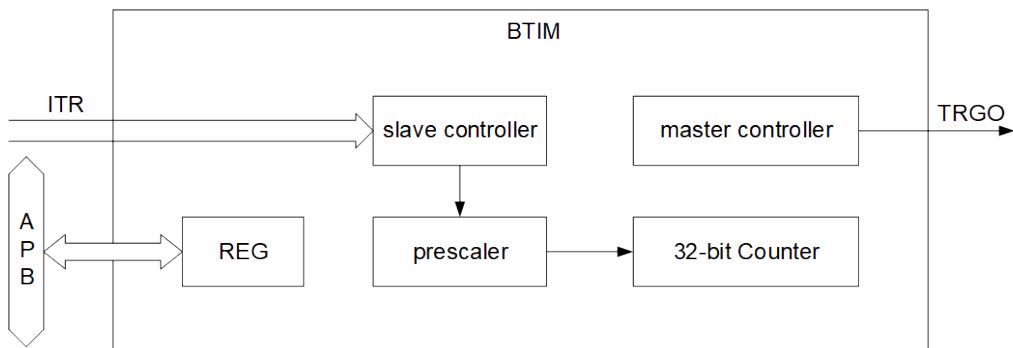

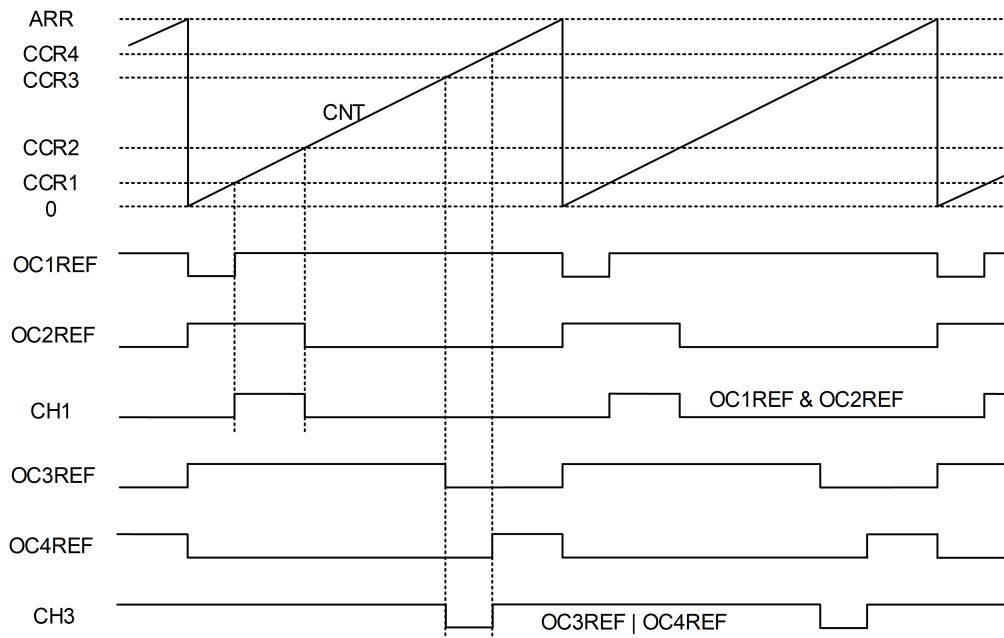

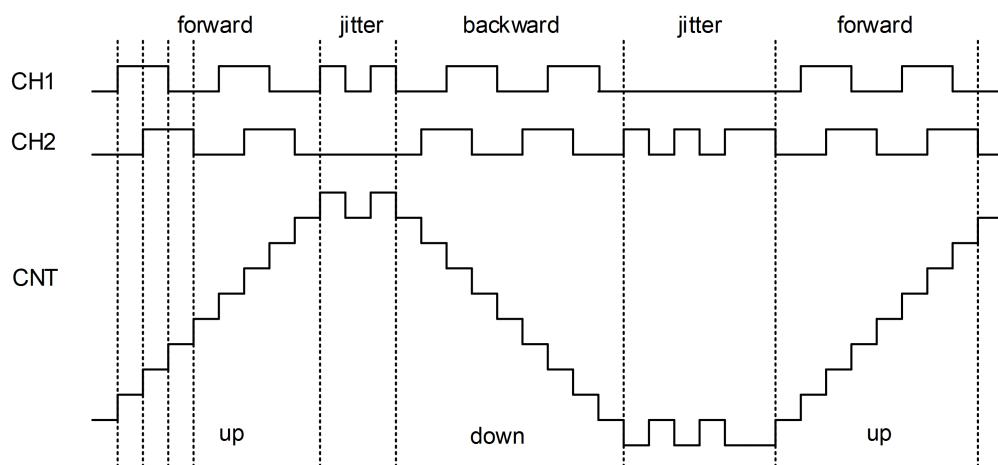

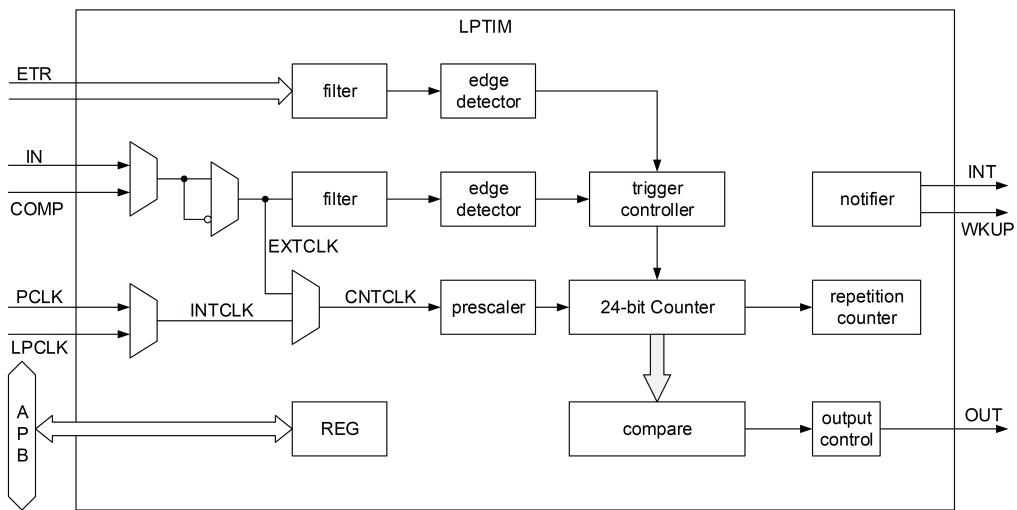

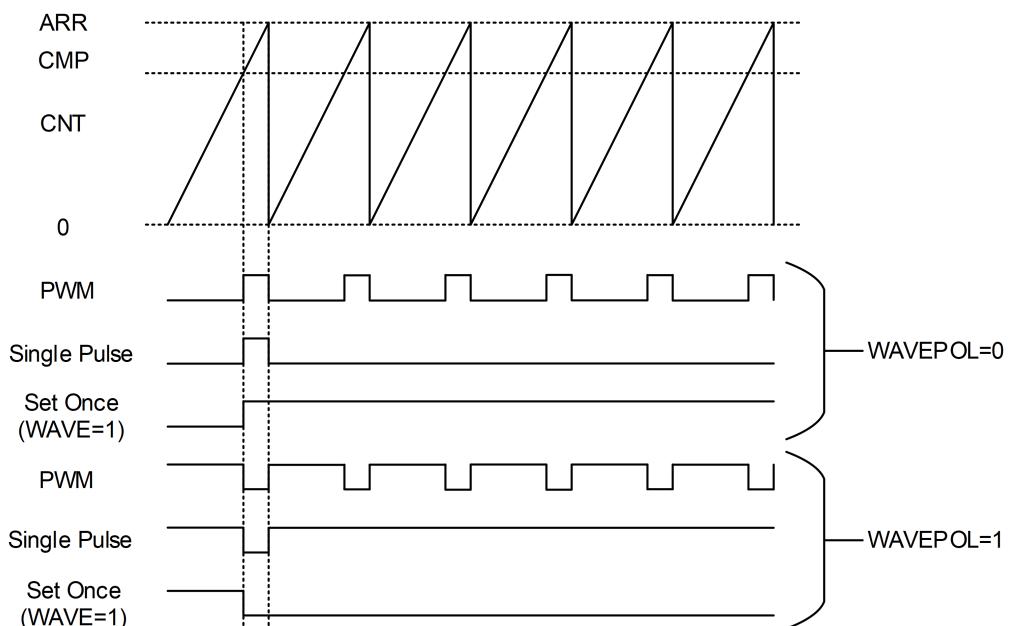

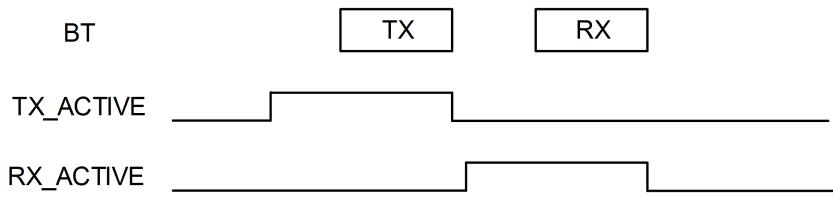

|            | <b>128KB</b>     |               | <b>0x5008_0000</b> | <b>0x5009_FFFF</b> | <b>0x5008_0000</b> | <b>0x5009_FFFF</b> |